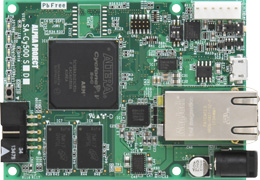

Intel® SoC アルファボードシリーズ

Intel® SoC搭載CPUボード

SA-Cy500S

¥50,000

(税込 ¥55,000)販売終了品

-

-

A9

600MHz - RAM

512MB - ROM

16MB

-

-

- Ethernet

- Wi-Fi

- Bluetooth

- USB

- SD

- LCD

- CAMERA

- CAN

SA-Cy500Sは、Intel®社製「Cyclone® V SoC」を搭載した小型CPUボードです。

Cyclone® V SoCは、Arm® Cortex®-A9をCPUコアとしたHPSと、FPGAファブリックを統合したSoCです。Gigabit Ethernet、USBなどの通信機能やCMOSカメラ入力、LCD出力インタフェースを備えており、通信機器や高度な画像処理用途に適しています。

本ボードは外部接続コネクタへ外部拡張に必要な信号を引き出してありますので、各種試作用途及び製品への組込み用途など、幅広い対応が可能です。

特長

- Arm Cortex-A9プロセッサ搭載

動作周波数 600MHz

- Cyclone®V FPGA

ロジックエレメント 25,000

- 大容量メモリを搭載(プログラムメモリ:QSPI Flash ROM 16MByte、データメモリ:DDR3 SDRAM 512MByte)

- Ethernetポートを搭載(10/100/1000BASE-T対応のEthernetコネクタを搭載)

- USBポートを搭載(USB OTG(High/Full/Low-Speed対応)を1ch搭載)

- シリアルインタフェースコネクタを装備、各種インタフェースコンバータを接続すれば、簡単にPCとの通信が可能

- JTAGコネクタを装備(USB Blaster用とCoreSight用の2つのJTAGコネクタを搭載)

- カメラインタフェース搭載

カメラインタフェースを搭載し、市販のカメラモジュールを接続可能です。

- LCDインタフェース搭載

タッチパネルLCD(WVGA,WQVGA)に対応。当社製LCDキットが直接接続できます。

- 抵抗膜式 7インチ WVGA LCDキット「LCD-KIT-C01」

- 静電容量式 4.3インチ WQVGA LCDキット「LCD-KIT-D02」

- 回路図、サンプルプログラムを提供

- Linux開発キットをご用意

| 組込みOS + ミドルウェア |

イー・フォース |

μITRON4.0仕様 RTOS「μC3/Standard」 μITRON4.0のスタンダードプロファイルに準拠し、32/64ビットプロセッサが搭載された組込みシステム向けのRTOSです。 組込みシステム向けのTCP/IPスタック「μNet3」 μC3と組合せて使用する組込みシステム向けのTCP/IPスタックです。 イー・フォースWebサイトにて |

仕様

| SoC | 5CSEBA2U23C8SN | |

|---|---|---|

| HPS | CPU | Cortex®-A9 シングルコア |

| クロック |

|

|

| メモリ |

|

|

| Ethernet I/F |

|

|

| USB I/F | CPU内蔵 USBコントローラ USB PHY USB3300(Microchip)

|

|

| SDカードI/F |

|

|

| シリアル I/F |

|

|

| FPGA | FPGA | Cyclone® V

|

| LCD I/F※1 | LCDインタフェースコネクタに接続(RGB666) | |

| カメラI/F※1 | カメラインタフェースコネクタに接続 | |

| LED |

|

|

| リセット | リセット IC、リセット SW 搭載、リコンフィギュレーションSW搭載 | |

| JTAG I/F |

|

|

| 外部接続 | 160pinコネクタ HPS端子19本、FPGA端子91本 |

|

| 電源※2 | DC5V ±5%(CPUコア:1.1V、I/O:3.3V) | |

| 消費電流 | Typ 750mA(弊社サンプルプログラム動作時) | |

| 動作環境 | 0~60℃(結露なし) | |

| 基板寸法 | 80×60mm(コネクタ、突起物除く) | |

| 付属品 | ヒートシンク | |

|

||

オプション

ダウンロード

ご注意ご使用の前にご確認ください。

- 弊社Webサイトより取得可能なサンプルプログラムは無償で提供されるものであり、あくまで評価用途です。

弊社がこの動作を保証するものではありません。サンプルプログラムを使用する場合、適切な環境でご使用ください。 - 弊社は、使用に起因する損害、第三者の権利を侵害に関し、いかなる責任も負いません。

本プログラムの使用、若しくは機能から生じるすべての損害は、ご使用になるお客様の負担となります。 - サンプルプログラムの仕様変更およびその他いかなる理由においても、弊社は、サンプルプログラムの誤り、機能不全または欠陥を修正する義務を負いません。

- サンプルプログラムに関するお問い合わせは、お受けできません。

ただし機能不全等があった場合には、【メールフォーム】よりご一報ください。可能な範囲でご回答します。 - ご使用の前に必ず、【サンプルプログラム使用規約】への同意をお願いします。

本規約に同意されない限り、プログラムを使用することはできません。

| マニュアル・ドキュメント | バージョン | 更新日 |

|---|---|---|

| SA-Cy500S ハードウェアマニュアル | 3.4 | 2023/10/02 |

| AN5101 SA-Cy500S(Cyclone V SoC CPU BOARD) スタートガイド | 2.1 | 2023/10/02 |

| AN5102 SA-Cy500S(Cyclone V SoC CPU BOARD) サンプルHDLプログラム解説 | 3.1 | 2023/10/02 |

製品ご購入後に公開される情報

| 回路図 | パスワード | バージョン | 更新日 |

|---|---|---|---|

| SA-Cy500S 回路図 | 2.1 | 2019/06/28 |

| サンプルプログラム | パスワード | バージョン | 更新日 |

|---|---|---|---|

| SA-Cy500S サンプルHDLプログラム | 2.0 | 2018/10/03 |

| SDカードイメージ | パスワード | バージョン | 更新日 |

|---|---|---|---|

| オールインワンSDカードイメージ | 1.4 | 2020/06/01 |

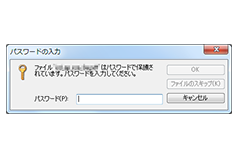

パスワードが必要なデータについて

-

1

購入製品の添付紙面よりパスワードをご確認ください。

-

2

公開情報一覧から必要な項目をクリックし、圧縮ファイルをダウンロードします。

-

3

圧縮ファイルを解凍する際、「1」に記載のパスワードをご入力ください。

製品をご購入済みで、パスワードが見つからないお客様

ユーザー登録を行っていない場合 お手数ですが、【ユーザー登録】を行い、備考欄に「パスワード希望」とご記載ください。

ユーザー登録がお済みの場合 お手数ですが、【メールフォーム】よりご連絡をお願いいたします。

なお、お問い合わせの際は「製品名」「シリアルナンバー」が必要となります。

ご購入

販売終了品

- ※ArmおよびCortexは、米国および/またはその他の地域におけるArm Limited(またはその子会社)の登録商標です。

- ※記載されている会社名、製品名は、各社の登録商標または商標です。

- ※記載の内容は改良のため、予告なく変更する場合がございます。