PC/104 規格準拠 SH-4A CPU ボード

# **MS104-SH4AG**

# Hardware Manual 6 版 ダイジェスト版

# ご使用になる前に

このたびは MS104-SH4AG をお買い上げいただき誠にありがとうございます。

本製品をお役立て頂くために、このマニュアルを十分お読みいただき、正しくお使いください。

今後共、弊社製品をご愛顧賜りますよう宜しくお願いいたします。

# 梱包内容

本製品は、下記の品より構成されております。梱包内容をご確認のうえ、万が一、不足しているものがあれば お買い上げの販売店までご連絡ください。

MS-104-SH4AG 梱包内容 -

●MS104-SH4AG 1 枚 ●14Pin MIL コネクタ 1 個 ●D-Sub 変換ケーブル 2 本 ●M3 x 16mm スペーサー 4 本

●M3 ナット 4 個

●マニュアル・サンプルプログラムのダウンロード・保証のご案内 1枚

■本製品の内容及び仕様は予告なしに変更されることがありますのでご了承ください。

# 取り扱い上の注意

●本製品には、民生用の一般電子部品が使用されており、一般的な民生用途の電子機器への使用を意図して 設計されています。宇宙、航空、医療、原子力、運輸、交通、各種安全装置などで人命、事故に関わる 用途および多大な物的損害を発生させる恐れのある用途でのご使用はご遠慮ください。

- ●極端な高温下や低温下、または振動の激しい環境での使用はご遠慮ください。

- ●水中、高湿度、油の多い環境でのご使用はご遠慮ください。

- ●腐食性ガス、可燃性ガス等の環境中でのご使用はご遠慮ください。

- ●基板の表面が水に濡れていたり、金属に接触した状態で電源を投入しないでください。

- ●定格を越える電源を加えないでください。

- ■ノイズの多い環境での動作は保証しかねますのでご了承ください。

- ■連続的な振動(車載等)や衝撃が発生する環境下でのご使用は、製品寿命を縮め、故障が発生しやすくなりますのでご注意ください。

- ■発煙や発火、異常な発熱があった場合には、すぐに電源を切ってください。

- ■本製品を仕様範囲を越える条件において使用した場合、故障の原因となりますので、ご注意ください。

- ■本書に記載される製品および技術のうち、「外国為替および外国貿易法」に定める規制貨物等(技術)に該当するものを輸出 または国外に持ち出す場合には同法に基づく輸出許可が必要です。

- ■本製品マニュアル、回路図及び HDL コードの著作権は株式会社アルファプロジェクトが保有しております。これらを無断で転用、 掲載、譲渡、配布することは禁止します。

# 保証

- ■保証期間内において、本マニュアル等に記載の注意事項に従い正常な使用状態で故障した場合、保証対象といたします。

- ■製品保証の内外を問わず、製品を運用した結果による、直接的および間接的損害については、弊社は一切補償いたしません。

- ■保証対象は、製品本体とします。ソフトウェア・マニュアル・消耗品・梱包箱は保証対象外とさせていただきます。

- ■本保証は日本国内においてのみ有効です。海外からのご依頼は受付しておりません。

- ■製品保証規定の詳細につきましては、ホームページをご覧ください。

# 参考資料

デバイスの資料は、各社ホームページで公開されております。本マニュアルと合わせて、ご覧ください。

■SH7764 シリーズハードウェアマニュアル ルネサス エレクトロニクス

■PC/104 Specification

PC/104 Consortium

■その他各社デバイスデータシート

# 参考URL

下記の URL に本製品に関連するデバイスおよび規格の情報が掲載されておりますので、参考にしてください。

■ルネサス エレクトロニクス株式会社

■Cypress Semiconductor

■Elite Semiconductor Memory Technology(ESMT)

■ザイリンクス株式会社

■PC/104 Consortium

■CompactFlash Association

■SD Association

https://www.renesas.com/jp/ja

https://japan.cypress.com/

https://www.esmt.com.tw/en

https://japan.xilinx.com/

https://pc104.org/

https://www.compactflash.org/

https://www.sdcard.org/ja/

# ソフトウェアについて

●本製品には、ソフトウェアは付属しません。

本製品で動作するソフトウェアについては、「5. 関連製品のご案内」をご覧ください。 ソフトウェアに関するライセンス、保証、免責事項については、各製品のマニュアルをご覧ください。

# 目 次

| 1. | 概要    |                          | 1  |

|----|-------|--------------------------|----|

|    | 1. 1  | 製品概要1                    |    |

|    | 1. 2  | 機能及び特長1                  |    |

|    | 1. 3  | 仕様概要                     |    |

|    | 1.4   | 外観3                      |    |

|    | 1.5   | 回路構成                     |    |

|    | 1.6   | アドレスマップ6                 |    |

| 2. | 機能    |                          | 7  |

|    | 2. 1  | CPU                      |    |

|    | 2. 2  | フラッシュメモリ10               |    |

|    | 2. 3  | SDRAM                    |    |

|    | 2. 4  | CPLD                     |    |

|    | 2. 5  | RTC(リアルタイムクロック)13        |    |

|    | 2. 6  | EEPROM                   |    |

|    | 2. 7  | 割り込み16                   |    |

|    | 2. 8  | ディップスイッチ18               |    |

| 3. | 外部    | インタフェース                  | 19 |

|    | 3. 1  | コンパクトフラッシュ19             |    |

|    | 3. 2  | SD メモリカード                |    |

|    | 3. 3  | イーサネットインタフェース24          |    |

|    | 3. 4  | USB ホストインタフェース           |    |

|    | 3. 5  | シリアルインタフェース27            |    |

|    | 3. 6  | LCD インタフェース              |    |

|    | 3. 7  | オーディオインタフェース32           |    |

|    | 3. 8  | I <sup>2</sup> C インタフェース |    |

|    | 3. 9  | 10 ポート                   |    |

|    | 3. 10 | デバッグインタフェース(H-UDI)36     |    |

|    | 3. 11 | PC/104 バスインタフェース         |    |

|    | 3. 12 | 電源45                     |    |

| 4. | テク   | ニカルデータ              | 46 |

|----|------|---------------------|----|

|    | 4. 1 | 外形寸法                |    |

|    | 4. 2 | PC/104 ボードの接続       |    |

|    | 4. 3 | DC 特性               |    |

| 5. | 関連   | 製品のご案内              | 49 |

|    | 5. 1 | Linux 開発キット         |    |

|    | 5. 2 | MS104 シリーズ機能拡張ボード49 |    |

|    | 5. 3 | AC アダプタ50           |    |

|    | 5. 4 | PC/104 コネクタ50       |    |

|    | 5. 5 | Flash 書き込みツール       |    |

| 6. | 製品   | サポートのご案内            | 52 |

MS104 Series

#### 概要 1.

#### 製品概要 1.1

MS104-SH4AG は、SH7764(ルネサス エレクトロニクス社製)を搭載したボードコンピュータです。多様なインタフェースを搭載 し、標準 OS に Linux を採用しているので、高度な組み込みアプリケーションを容易に構築することができます。 また、PC/104 規格に準拠\*1しているので、市販ボードを利用すること\*2ができ、拡張性に優れています。

## 1.2 機能及び特長

■ ルネサス エレクトロニクス社製 SH4A「SH7764 (R5S77640N300BG)」を搭載

SH7764 は SH-4A をコアとした浮動小数点ユニット(FPU)内蔵の高性能マイクロコントローラです。 最大動作周波数は 324MHz で、CPU は最大 538MIPS、FPU は単精度、倍精度演算をサポートし、最大 2.3GFLOPS を実現してい ます。また、周辺機能として、シリアルサウンドインタフェース、LCD コントローラ、イーサネットコントローラ、USB イ ンタフェース等を備え、マルチメディア機器、ネットワーク機器、医用機器、産業機器など、幅広い分野に利用する ことができます。

#### ■ 標準OSにLinuxを採用

標準OSにLinuxを採用することにより、高度なネットワーク機能や、ヒューマンインタフェースを備えた機器を容易に開発 することができます。また、世界中のプログラマによって日々開発される膨大なオープンソースソフトウェア資産をロイヤ リティフリーで利用することができます。

#### ■ FLASHROM16MByte、SDRAM64MByte搭載

#### ■ 多様なインタフェースを搭載

- EtherNET 10/100BASE-T

- USB2.0ホストインタフェース(Hi-Speed対応)

- CFカードスロット(UltraDMA対応)

- SD/MMCカードスロット

- 2CH 高速シリアルインタフェース

- LCDコントローラ

- 4CH ステレオ対応シリアルサウンドインタフェース

- I2Cインタフェース

- 8bit 汎用 GPIO

- H-UDI デバッグインタフェース

#### ■ PC/104規格準拠

#### ■ 周辺ボード

-MS104-LCD/AUDIO WQVGAタッチパネルLCD搭載 LCD/オーディオボード

-MS104-FPGA CycloneⅢ(Intel)搭載 FPGAボード

#### ■ 回路図を全て公開

- \*1 PC/104 規格と一部異なる部分があります。詳しくは PC/104 バスの説明をご覧ください。

- すべての PC/104 ボードとの互換性を保証するものではありません。 ソフトウェアは別途ご用意いただく必要があります。

- \*3

# 1.3 仕様概要

## MS104-SH4AG 仕様

| 機能                                                      | 仕 様                                                                                                                      |  |  |  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPU                                                     | R5S77640N300BG(BGA404) SH-4A コア<br>動作周波数: 324MHz 演算性能:CPU 583MIPS FPU 2.3GFLOPS<br>命令/オペランドキャッシュ 32KByte/32KByte         |  |  |  |

| クロック                                                    | システムクロック27.0000MHz 水晶発振器-CPU クロック最大 324MHz-バスクロック最大 108MHz-周辺クロック最大 54MHzRTC クロック32.768MHz 水晶振動子USB クロック48.0000MHz 水晶振動子 |  |  |  |

| メモリ                                                     | FLASHROM 16MByte(S29GL128P90TFIR20 Cypress 相当品)<br>SDRAM 64MByte(M12L2561616A-6TIG2S ESMT 相当品 2 個)                       |  |  |  |

| CPLD                                                    | XC9572XL-7TQ100C(Xilinx)                                                                                                 |  |  |  |

| イーサネットインタフェース                                           | CPU 内蔵イーサネットコントローラ<br>10/100BASE-T 1CH<br>EtherNET トランシーバ DP83848J(NS)                                                   |  |  |  |

| USB インタフェース                                             | CPU 内蔵 USB コントローラ<br>USB2.0 HOST(HIGH/FULL/LOW SPEED) 1 チャネル                                                             |  |  |  |

| CF カードスロット                                              | CPU 内蔵 ATAPI インタフェース<br>TYPE I 1 スロット<br>3.3V 専用 TruelDE モード UltraDMA 対応                                                 |  |  |  |

| SD/MMC カードスロット                                          | 1スロット SPIモード                                                                                                             |  |  |  |

| LCD コントローラ                                              | CPU 内蔵 LCD コントローラ<br>最大解像度 1024x1024dot                                                                                  |  |  |  |

| オーディオインタフェース                                            | CPU 内蔵シリアルサウンドインタフェース<br>ステレオ対応 4 チャネル                                                                                   |  |  |  |

| シリアル I/F                                                | CPU 内蔵シリアルインタフェース<br>調歩同期式 2 チャネル(RS232C レベル)<br>RS232C トランシーバ SP3232EUCA(Sipex)                                         |  |  |  |

| I2C インタフェース                                             | CPU 内蔵 I2C インタフェース                                                                                                       |  |  |  |

| パラレルインタフェース                                             | I/O 8bit 3.3V CMOS                                                                                                       |  |  |  |

| モニタ LED                                                 | 赤 1 個(RESET モニタ) 緑 2 個(モニターLED) CPLD に接続                                                                                 |  |  |  |

| デバッグインタフェース                                             | H-UDI                                                                                                                    |  |  |  |

| RTC                                                     | S-35190(SII)<br>電気二重層コンデンサによりバックアップ (バックアップ時間 約 645 時間)<br>外部バックアップ電源によるバックアップ可能                                         |  |  |  |

| リセット                                                    | リセット IC、リセット SW 搭載                                                                                                       |  |  |  |

| 外部拡張バス                                                  | PC/104 準拠(一部非サポート)                                                                                                       |  |  |  |

| 電源電圧 DC JACK(EIAJ 標準 2.1mm)5.0V±5%(CPU コア 1.2V I/O 3.3V |                                                                                                                          |  |  |  |

| オプション電源                                                 | DC -5V、+12V、-12V                                                                                                         |  |  |  |

| 消費電流                                                    | Typ 350 mA (弊社サンプルプログラム動作時)                                                                                              |  |  |  |

| 使用環境条件                                                  | 温度 0℃~50℃ 湿度 70%(結露なし)                                                                                                   |  |  |  |

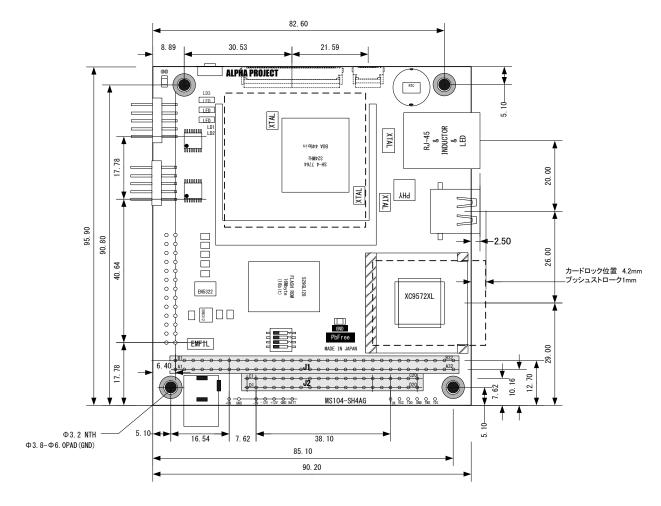

| 寸法                                                      | 90.2×95.9 mm                                                                                                             |  |  |  |

Table 1.3-1 仕様概要

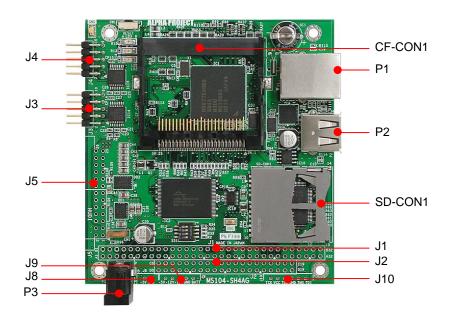

# 1.4 外観

Fig 1.4-1 外観(部品面)

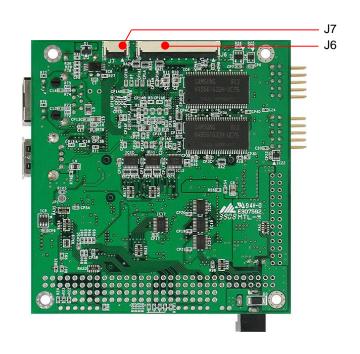

Fig 1.4-2 外観(ハンダ面)

| コネクタ番号  | コネクタ型番/メーカー           | 用途                              | 備考  |

|---------|-----------------------|---------------------------------|-----|

| J1      | PC104-64HK            | PC104 コネクタ                      | 未実装 |

| J2      | PC104-40HK            | PC104 コネクタ                      | 未実装 |

| J3、J4   | XG8B-1034/OMRON       | シリアル I/F コネクタ                   |     |

| J5      | XG4C-2634/OMRON       | DIO/H-UDI コネクタ                  | 未実装 |

| J6      | XF2M-5015-1A/OMRON    | LCD I/F、AUDIO I/F、I2C 拡張コネクタ    |     |

| J7      | XF2M-1015-1A/OMRON    | AUDIO I/F コネクタ                  |     |

| J8      | B2B-EH/日圧             | 電源コネクタ                          | 未実装 |

| J9      | B5B-EH/日圧             | オプション電源コネクタ                     | 未実装 |

| J10     | B6B-EH/日圧             | JTAG(CPLD)コネクタ                  | 未実装 |

| P1      | PTL-TJ-N-D/ジロテック      | EtherNET コネクタ                   |     |

| P2      | CU01SAH1S00/Cvilux    | USB 標準 A コネクタ                   |     |

| P3      | MJ-179P-ROHS/マルシン無線   | DC ジャック(2.1mm (内径) 5.5mm (外径) ) |     |

| SD-CON1 | SCDA4A0400/アルプス電気     | SD カードコネクタ                      |     |

| CF-CON1 | MI21A-50PD-SF(71)/ヒロセ | CF コネクタ                         |     |

使用コネクタは、相当品に変更される場合がありますので、ご了承ください。

Table 1.4-1 コネクタ一覧

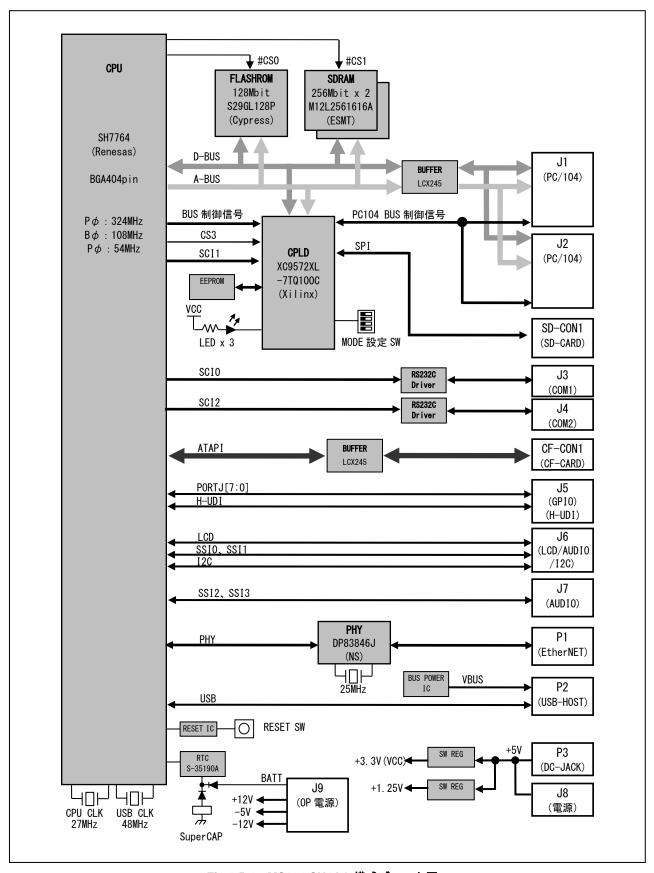

## 1.5 回路構成

Fig 1.5-1 MS104-SH4AG 構成ブロック図

# 1.6 アドレスマップ

\_ メモリアドレスマップ

| 領域       | アドレス(P0)   | アドレス(P2)   | デバイス           | BSC 設定   |

|----------|------------|------------|----------------|----------|

| エリア 0    | H'0000000  | H'A000000  | FlashROM       | 16bit    |

| (CS0 空間) | H'00FFFFF  | H'AOFFFFF  | 16Mbyte        | 通常メモリ空間  |

|          | H'01000000 | H'A1000000 | イメージ           |          |

|          | H'03FFFFF  | H'A3FFFFF  |                |          |

| エリア 1    | H'0400000  | H'A4000000 | SDRAM          | 32bit    |

| (CS1 空間) | H'07FFFFF  | H'A7FFFFF  | 64Mbyte        | SDRAM 空間 |

| エリア 2    | H'08000000 | H'A8000000 | 未使用            | 32bit    |

| (CS2 空間) | H'0BFFFFF  | H'ABFFFFF  |                | SDRAM 空間 |

| エリア 3    | H'0C000000 | H'AC000000 | PC/104 メモリ空間   | 8/16bit  |

| (CS3 空間) | H'0CFFFFF  | H'ACFFFFF  |                | 通常メモリ空間  |

|          | H'0D000000 | H'AD00000  | PC/104 IO 空間   |          |

|          | H'0D00FFFF | H'AD00FFFF |                |          |

|          | H'0D000000 | H'AD010000 | PC/104 IO 空間   |          |

|          | H'0D3FFFF  | H'AD3FFFFF | イメージ           |          |

|          | H'0D40000  | H'AD40000  | 周辺制御レジスタ(CPLD) |          |

|          | H'0FFFFFF  | H'AFFFFFF  |                |          |

P0 = P0 領域(キャッシュ領域) P2 = P2 領域(ノンキャッシュ領域)

Fig 1.6-1 アドレスマップ

# 2. 機能

# 2.1 CPU

### 2.1.1 動作モードの設定

MS104-SH4AG の SH7764 の MODE 端子は、出荷時には次の設定となっています。

| 端子    | 設定値 |                |                 |      |     |     |               |  |

|-------|-----|----------------|-----------------|------|-----|-----|---------------|--|

| MODE0 | 1   | クロック動作モード      | 3               |      |     |     | 固定            |  |

| MODE1 | 1   |                |                 |      |     |     | lck=コアクロック    |  |

| MODE2 | 0   | クロック           | lck             | SHck | Bck | Pck | SHck=内部バスクロック |  |

|       |     | 周波数比           | 周波数比 12 4 4 2   |      |     |     | Bck=外部バスクロック  |  |

|       |     | 最大周波数(MHz)     | 324             | 108  | 108 | 54  | Pck=周辺クロック    |  |

|       |     |                |                 |      |     |     |               |  |

| MODE3 | 0   | エリア 0 バス幅 16bi | エリア 0 バス幅 16bit |      |     |     |               |  |

| MODE4 | 1   |                |                 |      |     |     |               |  |

| MODE5 | 1   | リトルエンディアン      |                 |      |     |     | SS1-1 で設定     |  |

| MODE8 | 1   | 水晶発振子          |                 |      |     | •   | 固定            |  |

Table 2.1-1 動作モードの設定

## 2.1.2 エンディアンの設定

SH7764 のエンディアン設定(MODE5) はスイッチ (SS1-1) の設定により切り替えができます。 ディップスイッチの設定については、「2.8 ディップスイッチ」をご覧ください。

#### Linux での設定について

弊社が提供する Linux を動作させる場合には、必ずリトルエンディアンの設定としてください。 ビッグエンディアンには対応していません。

### 2.2 フラッシュメモリ

MS104-SH4AGには、標準で16MbyteのNOR FLASH (S29GL128P(Cypress))が搭載されています。 SH7764のCSO空間に16bitバスで接続されており、ブートメモリとして機能します。

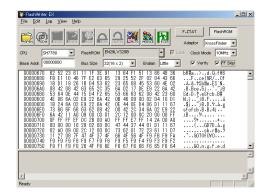

#### 2.2.1 フラッシュメモリの書き込み方法

フラッシュメモリの書き込み方法には、次の二つの方法がありますなお、フラッシュメモリへの書き込みを行う場合は、ディップスイッチ(SS1-2)で書き込み許可に設定してください。 ディップスイッチの設定については、「2.8 ディップスイッチ」をご覧ください。

#### -H-UDI (JTAG) を利用して書き込む

H-UDI インタフェース経由で書き込む方法です。フラッシュメモリに何も書かれていない初期状態でもオンボードで書き込むことが可能です。弊社製品「FlashWriterEX」や H-UDI デバッガのフラッシュ書き込み機能がこれに該当します。

#### - ブートプログラム等のプログラムの書き込み機能を利用する

あらかじめ書き込まれたプログラムによって、シリアルインタフェースやフラッシュメモリカード等からプログラムを 読み込んで書き込む方法です。U-Boot や Linux のフラッシュ書き込み機能等がこれに該当します。

#### 2.3 SDRAM

MS104-SH4AG には、標準で 64Mbyte の SDRAM(M12L2561616A(ESMT))が搭載されています。 SH7764 の CS1 空間に 32bit バスで接続されており、メインメモリとして機能します。

## 2.4 CPLD

MS104-SH4AG は、CPU 周辺ロジック用に CPLD (XC9572XL (XILINX)) を搭載しています。

XC9572XL は内部が FLASH メモリベースとなっており、オンボードで内部ロジックの書き換えが可能です。

MS104-SH4AG では、主に次の機能を CPLD でおこなっています。

- CPU 動作モードの設定

- 割り込み制御

- SDメモリカード制御

- PC/104 バスブリッジ

- EEPROM 制御

内部ロジックは、VelirogHDLで記述されています。添付のソースコードファイルを参照してください。

開発ツール : Xilinx ISE9.1i プロジェクト名 : MS104-SH4AG.ise Velilog ファイル名 : MS104\_SH4AG\_XXX.v

XXX はバージョンによって変わります。

#### CPLD の開発ツール

CPLD の開発ツールは、XILINX より無償提供されている ISE WebPack を利用することができます。 詳しくは、XILINX 社のホームページをご覧ください。

XILINX 社 WEB サイト <a href="https://japan.xilinx.com/">https://japan.xilinx.com/</a>

#### CPLD の書き換え

CPLD の書き換えは、XILINX 社製のダウンロードケーブルを JTAG コネクタ(J10)に接続して行います。JTAG コネクタは未 実装となっておりますので、2.54mm ピッチのヘッダピン等を実装して接続してください。

\* CPLD の書き換えは、自己責任でお願いいたします。

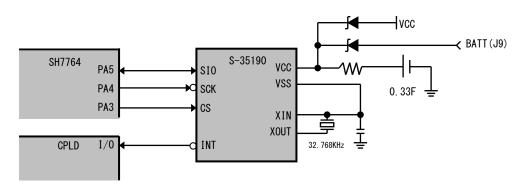

# 2.5 RTC(リアルタイムクロック)

MS104-SH4AG は、時計用として RTC を搭載しています。バックアップ回路を搭載しており、電源を遮断しても、計時動作を維持することができます。

| 機能            | 仕様                 |

|---------------|--------------------|

| デバイス          | S-35190(セイコーインスツル) |

| オンボードバックアップ電源 | 電気二重層コンデンサ 0.33F   |

|               | 充電時間:約 300 秒       |

|               | バックアップ時間 約 645 時間  |

| 外部バックアップ電源    | コネクタより供給可能         |

Table 2.5-1 RTC 仕様

## 2.5.1 RTC のインタフェース

RTC は、3 線シリアルインタフェースとなっており、CPU 内蔵 I/O ポートにより通信します。

Fig 2.5-1 RTC 接続図

|         |      | ポート |                                 |

|---------|------|-----|---------------------------------|

| RTC 信号名 | ポート  | 入出力 | 機能                              |

| SIO     | PA5  | I/O | シリアルデータ入出力信号。                   |

|         |      |     | CPU ポートは、入出力を切り替えて通信をおこなってください。 |

| SCK     | PA4  | 0   | クロック信号 4Hz~200KHz               |

| CS      | PA3  | 0   | チップセレクト信号 High アクティブ            |

| INT     | CPLD | I   | 「2.7割り込み」を参照してください。             |

## 2.6 EEPROM

MS104-SH4AG は、パラメータ保存用として 1KbitEEPROM を搭載しています。ネットワーク設定の保存や、各種パラメータの保存に利用できます。

| 機能   | 仕様                       |

|------|--------------------------|

| デバイス | 93LC46B (16bit x 64Word) |

|      | 書き換えサイクル 1,000,000 回     |

|      | データ保持期間 200 年以上          |

Table 2.6-1 EEPROM 仕様

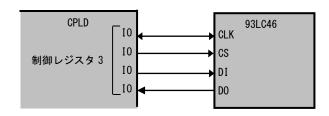

## 2.6.1 EEPROM のインタフェース

EEPROM は、4線シリアルインタフェースとなっており、CPLD の IO 信号に接続されています。

Fig 2.6-1 EEPROM 接続図

制御レジスタ 3 (H'AE000000) 初期値 =x0H

| D7                                       | D6  | D5      | D4       | D3       | D2     | D1         | D0     |  |

|------------------------------------------|-----|---------|----------|----------|--------|------------|--------|--|

| -                                        | -   | -       | -        | EEP_DO   | EEP_DI | EEP_CLK    | EEP_CS |  |

|                                          |     |         |          | R        | R/W    | R/W        | R/W    |  |

| EEP_CS : CS(チップセレクト)信号を制御します。 1:High レベル |     |         |          |          |        |            |        |  |

|                                          |     |         |          |          | 0      | ):Low レベル  |        |  |

| EEP_CLK : CLK(クロック)信号を制御します。             |     |         |          |          |        | 1:High レベル |        |  |

|                                          |     |         |          |          | 0      | にLow レベル   |        |  |

| EEP_DI : DI (データ入力) 信                    |     |         | 力)信号を制   | 御します。    | 1      | :High レベル  |        |  |

|                                          |     |         |          |          | 0      | ):Low レベル  |        |  |

| EEP_DO                                   | : [ | DO(データ出 | 出力) 信号の料 | 犬態を示します。 | 1      | :High レベル  |        |  |

|                                          |     |         |          |          | 0      | ):Low レベル  |        |  |

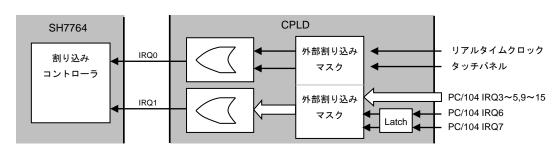

## 2.7 割り込み

## 2.7.1 外部割り込みの割り当て

MS104-SH4AGの外部割り込みは、IRQ割り込みを使用しています。外部割り込みは次のように割り当てられています。

| 割り込み端子       | 割り込み端子設定      | 割り込みデバイス                   | 割り込み検出レベル |

|--------------|---------------|----------------------------|-----------|

| IRQ0 LOW レベル |               | リアルタイムクロック                 | LOW レベル   |

|              | ICR1.IRQ0S=10 | タッチパネルコントローラ <sup>*1</sup> | LOW レベル   |

| IRQ1         | LOW レベル       | PC104 IRQ15                | HIGH レベル  |

|              | ICR1.IRQ1S=10 | PC104 IRQ14                | HIGH レベル  |

|              |               | PC104 IRQ12                | HIGH レベル  |

|              |               | PC104 IRQ11                | HIGH レベル  |

|              |               | PC104 IRQ10                | HIGH レベル  |

|              |               | PC104 IRQ9                 | HIGH レベル  |

|              |               | PC104 IRQ7                 | 立ち上がりエッジ  |

|              |               | PC104 IRQ6                 | 立ち上がりエッジ  |

|              |               | PC104 IRQ5                 | HIGH レベル  |

|              |               | PC104 IRQ4                 | HIGH レベル  |

|              |               | PC104 IRQ3                 | HIGH レベル  |

Table 2.7-1 外部割り込み一覧

\*1 MS104-LCD/AUDIO 使用時

#### 2.7.2 外部割り込み回路の構成

MS104-SH4AG の割り込みは、次のような構成になっています。

Fig 2.7-1 割り込み回路の構成

MS104-SH4AG の割り込みは、2本の IRQ 端子を複数の割り込みで共有(優先順位なし)しています。 したがって、割り込みを使用する場合には、ソフトウェアで周辺制御レジスタより割り込みステータスを読み込んで、割り込みデバイスを特定する処理を行ってください。

#### 2.7.3 PC/104 バスの割り込み

PC/104 バスの割り込みは、 $IRQ3\sim IRQ15$  までの計 11 本で、これらはすべて IRQ1 に 0R 入力されています。

通常、PC/104 準拠のボードは割り込み出力が High レベルとなっていますが、一部の市販ボードでは、割り込み出力がエッジ出力 (パルス出力) になっている製品があります。MS104-SH4AG では、それらに対応するために IRQ6 と IRQ7 が立ち上がりエッジに対応した入力となっています。

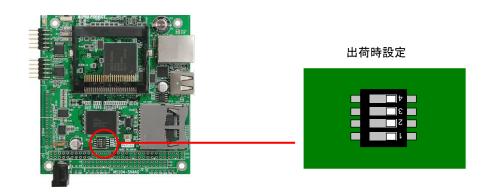

# 2.8 ディップスイッチ

MS104-SH4AGには、動作モード等を設定するためのディップスイッチがあります。 ボードを動作させる前に、必ず設定をご確認ください。

| スイッチ  | 設定  | 機能                    |

|-------|-----|-----------------------|

|       | 0FF | CPU MODE5=HIGH        |

| SS1-1 |     | リトルエンディアン             |

|       | ON  | CPU MODE5=LOW         |

|       |     | ビッグエンディアン             |

|       | 0FF | FLASHROM              |

| SS1-2 |     | 書き込み禁止                |

|       | ON  | FLASHROM              |

|       |     | 書き込み許可                |

|       | 0FF | PC/104 バスモード          |

| SS1-3 |     | SYSCLK 出力 7.714286MHz |

|       | ON  | SHバスモード               |

|       |     | SYSCLK 出力 108MHz      |

|       | 0FF | ユーザ開放                 |

| SS1-4 |     | 制御レジスタ 0              |

|       | ON  | ユーザ開放                 |

|       |     | 制御レジスタ 0              |

Fig 2.8-1 ディップスイッチの設定

# 3. 外部インタフェース

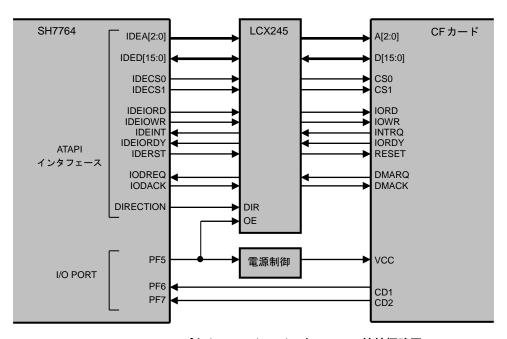

## 3.1 コンパクトフラッシュ

MS104-SH4AG は、コンパクトフラッシュ TYPE I/Ⅱ対応スロットを1スロット搭載しています。

インタフェースは True IDE モードで、アクセスモードは PIO モードとマルチワード DMA モードと UltraDMA モードに対応しています。

電源は3.3Vで、活線挿抜\*\*1に対応しているので、電源を投入したままでコンパクトフラッシュカードの抜き差しが可能です。 \*1 ソフトウェアの対応が必要です。

| 機能             | 仕様                                                                                                              |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| コンパクトフラッシュスロット | TYPE I / Ⅱ 対応 3.3V 専用                                                                                           |

| インタフェース        | TreuIDE モード                                                                                                     |

| アクセスモード        | PIO モード モード 0~4                                                                                                 |

|                | マルチワード DMA モード 0~2                                                                                              |

|                | Ultra DMA モード モード 0~4                                                                                           |

| 転送速度(参考値)      | UltraDMA モード 4 の場合                                                                                              |

|                | 実測値 リード:約 39Mbyte/sec ライト: 約 13.5Mbyte/sec<br>Linux(Kernel2.6.25)上で弊社テストプログラムにて測定した参考値<br>使用環境やソフトウェアによって変動します。 |

Table 3.1-1 コンパクトフラッシュインタフェース仕様

#### 3.1.1 コンパクトフラッシュのインタフェース

コンパクトフラッシュのインタフェース信号は、バッファ ICを介して CF スロットに接続されています。

Fig 3.1-1 コンパクトフラッシュインタフェース接続概略図

## 3.2 SD メモリカード

MS104-SH4AG は、SD/MMC カードスロットを1スロット搭載しています。インタフェースは SPI モードで、活線挿抜\*1に対応しているので、電源を投入したままで SD メモリカードの抜き差しが可能です。 \*1 ソフトウェアの対応が必要です。

| 機能             | 仕様                                                                                                          |

|----------------|-------------------------------------------------------------------------------------------------------------|

| SD/MMC カードスロット | プッシュロック式 1スロット                                                                                              |

| インタフェース        | SPI モード                                                                                                     |

| 対応メモリカード       | SD メモリカード・SDHC メモリカード・MMC                                                                                   |

| アクセス速度(参考値)    | SPI モード 同期クロック 4.5MHz の場合                                                                                   |

|                | 実測値 リード:約 153kbyte/sec ライト: 約 144kbyte<br>Linux(Kernel2.6.25)上で弊社テストプログラムにて測定した参考値<br>使用環境やソフトウェアによって変動します。 |

Table 3.2-1 SD メモリカードインタフェース仕様

#### SD メモリカードのライセンスについて

SD メモリカードのインタフェースには、SD カードモードと SPI モードがあります。SD カードモードを利用する場合、SD アソシエーションのライセンスが必要となりますが、MS104-SH4AG で採用している SPI モードは、一般に仕様が公開されており、ライセンスは不要です。

#### 3.2.1 SD メモリカードのインタフェース

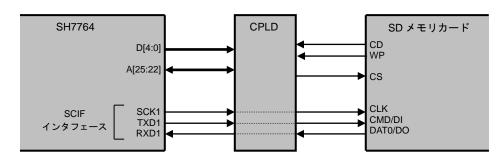

SDメモリカードのインタフェース信号は、SH7764の SCIF インタフェースに接続されています。

Fig 3.2-1 SD メモリカードインタフェース接続概略図

| PinNo | SD<br>信号名 | I/O | MS104-SH4AG<br>接続信号 | PinNo | SD<br>信号名 | I/O | MS104-SH4AG<br>接続信号 |

|-------|-----------|-----|---------------------|-------|-----------|-----|---------------------|

| 1     | DAT3/CS   | Ю   | CPLD:制御レジスタ 2       | 8     | DAT1      | -   | 10KΩPULL-UP         |

| 2     | CMD/DI    | 0   | TXD1                | 9     | DAT2      | -   | 10KΩPULL-UP         |

| 3     | GND       | Р   | GND                 | 10    | CD        | I   | CPLD:制御レジスタ 2       |

| 4     | VCC       | Р   | VCC                 | 11    | COMMON    | Р   | GND                 |

| 5     | CLK       | Ю   | SCK1                | 12    | WP        | I   | CPLD:制御レジスタ 2       |

| 6     | GND       | Р   | GND                 | 13    | GND       | Р   | GND                 |

| 7     | DAT0/DO   | -   | RXD1                |       |           |     |                     |

I:入力 O:出力 IO:入出力 P:電源

Table 3.2-2 SD メモリカードインタフェースピンアサイン

# 3.3 イーサネットインタフェース

MS-104-SH4AG は、10/100BASE-TX 対応の EtherNet インタフェースを 1 ポート備えています。 SH7764 内蔵のイーサネットコントローラを使用します。

| 機能          | 仕様                                                            |

|-------------|---------------------------------------------------------------|

| ポート構成       | 10/100BASE-TX 1 ポート                                           |

| コネクタ(P1)    | RJ-45 コネクタ 8pin                                               |

| MAC 層コントローラ | SH7764 内蔵コントローラ                                               |

| PHY 層コントローラ | DP83848J (NS)                                                 |

| 通信速度(参考値)   | 実測値 約 61Mbps<br>Linux(Kernel2.6.25)上で弊社テストプログラム(NFS)にて測定した参考値 |

|             | 使用環境やソフトウェアによって変動します。                                         |

Table 3.3-1 イーサネットインタフェース仕様

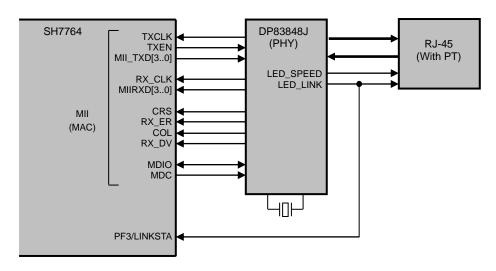

### 3.3.1 イーサネットインタフェースの構成

SH7764 と外部 PHY コントローラは、MII で接続されます。

Fig 3.3-1 イーサネットインタフェース接続概略図

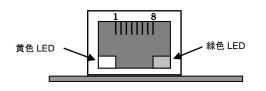

| No | 信 <del>号</del> | No | 信号  |

|----|----------------|----|-----|

| 1  | TX+            | 5  | -   |

| 2  | TX-            | 6  | RX- |

| 3  | RX+            | 7  | ı   |

| 4  | ı              | 8  | ı   |

Fig 3.3-2 LAN ポートコネクタ(P1 正面)

## 3.4 USB ホストインタフェース

MS-104-SH4AG は、USB2.0 ホストインタフェースを1ポート備えています。SH7764内蔵のUSBコントローラを使用します。

| 機能       | 仕様                                                  |

|----------|-----------------------------------------------------|

| ポート構成    | USB2.0 ホスト 1 ポート                                    |

| コネクタ(P2) | 標準 A コネクタ                                           |

| コントローラ   | SH7764 内蔵 USB コントローラ                                |

|          | -High(480Mbps) / Full(12Mbps) / Low(1.5Mbps) スピード対応 |

|          | -コントロール転送、バルク転送、インタラプト転送、アイソクロナス転送 対応               |

|          | -最大 10 本のパイプ                                        |

| VBUS 制御  | MIC2026-2YM(Micrel)                                 |

|          | - 最大 500mA - ON/OFF 制御 - 過電流検出機能                    |

| アクセス性能   | HIGH スピード対応 USB メモリのリード/ライト                         |

| (参考値)    | 実測値 リード:約 8.5Mbyte/sec ライト: 約 6.3Mbyte              |

|          | Linux(Kernel2.6.25)上で弊社テストプログラムにて測定した参考値            |

|          | 使用環境やソフトウェアによって変動します。                               |

Table 3.4-1 USB インタフェース仕様

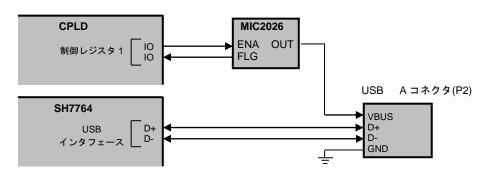

#### 3.4.1 USB ホストインタフェースの構成

USB ホストインタフェースは、次のような構成となっています。

Fig 3.4-1 USB ホストインタフェース接続概略図

MIC2026 の ENA と FLG の各信号は CPLD に接続されており、制御レジスタ 1 で制御します。

制御レジスタ 1 (H'AD800000) 初期値 =x0H

| D7 | D6 | D5 | D4 | D3 | D2             | D1      | D0      |

|----|----|----|----|----|----------------|---------|---------|

| -  | -  | -  | -  | 0  | COM2<br>ENABLE | USB_FLG | USB-ENA |

|    |    |    |    | R  | R/W            | R       | R/W     |

| USB_ENA | : VBUS 電源の ON/OFF を制御します。                    | 1:VBUS ON  |

|---------|----------------------------------------------|------------|

|         |                                              | 0:VBUS OFF |

| USB_FLG | : VBUS 電源の過電流を検出します。I <sub>VBUS</sub> >500mA | 1:過電流有     |

|         |                                              | 0:過電流無     |

## 3.5 シリアルインタフェース

MS-104-SH4AG は、シリアルインタフェースを2ポート備えています。SH7764内蔵のSCIFを使用します。

| 機能          |                    | 仕様                          |

|-------------|--------------------|-----------------------------|

| ポート構成       | RS232 レベル 27       | <b>ポート</b>                  |

| コネクタ(J3,J4) | 10pin (5x2 列)2.54m | ım ピッチヘッダピン                 |

|             | 9pin D-sub 変換ケー    | -ブルを接続して使用                  |

| コントローラ      | SH7764 内蔵 FIFO     | 内蔵シリアルコミュニケーションインタフェース      |

| インタフェース信号   | COM1               | TXD,RXD                     |

|             | COM2               | TXD,RXD,RTS,CTS             |

| 通信機能        | 通信方式               | 非同期通信                       |

|             | 通信速度               | 最高 1000Kbps サポート            |

|             | データ長               | 7 ビット /8 ビット                |

|             | ストップビット長           | 1 ビット /2 ビット                |

|             | パリティ               | 偶数/奇数/なし                    |

|             | 受信エラー検出            | パリティエラー、フレーミングエラー、オーバーランエラー |

Table 3.5-1 シリアルインタフェース仕様

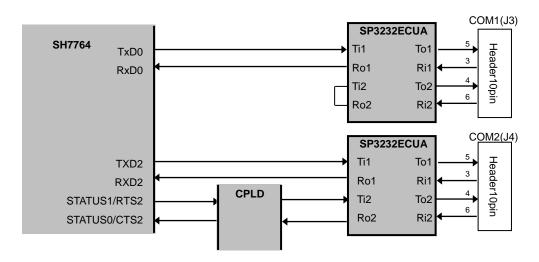

#### 3.5.1 シリアルインタフェースの構成

SH7764 のシリアルインタフェース信号は、RS232 ドライバを介して COM ポートに接続されます。

COM1(J3) ピンアサイン

| No. | 信号名  | I/O | No. | 信号名 | I/O |

|-----|------|-----|-----|-----|-----|

| 1   | N.C  | -   | 2   | N.C | -   |

| 3   | RxD0 | 1   | 4   | 短絡  | 0   |

| 5   | TxD0 | 0   | 6   | 短絡  | ı   |

| 7   | N.C  | -   | 8   | N.C | -   |

| 9   | GND  | -   | 10  | N.C | -   |

COM2(J4) ピンアサイン

| 33 <u>(3.)</u> |      |     |     |      |     |  |

|----------------|------|-----|-----|------|-----|--|

| No.            | 信号名  | I/O | No. | 信号名  | I/O |  |

| 1              | N.C  | -   | 2   | N.C  | -   |  |

| 3              | RxD2 | 1   | 4   | RTS2 | 0   |  |

| 5              | TxD2 | 0   | 6   | CTS2 |     |  |

| 7              | N.C  | -   | 8   | N.C  | -   |  |

| 9              | GND  | 1   | 10  | N.C  | ı   |  |

Fig 3.5-1 シリアルインタフェース回路構成図

# 3.6 LCD インタフェース

MS-104-SH4AG は、各種 LCD パネルに対応した LCD コントローラを備えています。 SH7764 は LCDC と VDC2 の 2 種類のコントローラを内蔵しており、どちらかを使用できます。

| 機能       | 仕様                                 |  |  |  |

|----------|------------------------------------|--|--|--|

| コネクタ(J6) | 50pin FPC コネクタ XF2M-5015-1A(OMRON) |  |  |  |

|          | -ロック機構                             |  |  |  |

|          | - 0.5mm ピッチ                        |  |  |  |

|          | -上下両接点タイプ                          |  |  |  |

|          | -適合 FPC t=0.3mm                    |  |  |  |

| コントローラ   | LCDC                               |  |  |  |

|          | -STN/TFT パネル対応                     |  |  |  |

|          | -4/8/15/16bpp カラーモード               |  |  |  |

|          | -16x1~1024x1024dot 液晶パネルサポート       |  |  |  |

|          | -RGB565 出力                         |  |  |  |

|          | -ドットクロック MAX54MHz                  |  |  |  |

|          | VDC2                               |  |  |  |

|          | -TFT パネル対応                         |  |  |  |

|          | -4 画面レイヤ                           |  |  |  |

|          | -外部同期モードサポート                       |  |  |  |

|          | -RGB666 出力                         |  |  |  |

|          | -ドットクロック MAX36MHz                  |  |  |  |

Table 3.6-1 LCD インタフェース仕様

### 表示サイズについて

SH7764 の LCDC および VDC2 での表示可能サイズは下記の計算式にて求めることができます。

ルネサス社の資料ではバス占有率が 40%以下になるように推奨されています。ただし、バス負荷が高いプログラムを実行 した場合には、画面表示が破綻する可能性がありますので、十分留意してください。

$$2.0 \times$$

水平表示ドット数 x 垂直表示ライン数 x フレームレート(Hz) x 色数(bpp) バス占有率(%) =

108MHz(CLKOUT) x 32bit(バス幅)

| 表示サイズ    | フレームレート |        |        | 備考                           |

|----------|---------|--------|--------|------------------------------|

| (16bpp)  | 40Hz    | 50Hz   | 60Hz   |                              |

| 320x240  | 2.85%   | 3.56%  | 4.27%  | 左記はレイヤ数1面の場合です。VDC2 で複数      |

| 480x270  | 4.80%   | 6.00%  | 7.20%  | レイヤ使用する場合には、レイヤ数を掛けてく        |

| 640x480  | 11.38%  | 14.22% | 17.07% | ださい。                         |

| 800x480  | 14.22%  | 17.78% | 21.33% | また、フレームレートが遅い場合、パネルによ        |

| 800x600  | 17.78%  | 22.22% | 26.67% | │ ってはフリッカが発生する可能性があります。<br>│ |

| 1024x768 | 29.13%  | 36.41% | 43.70% |                              |

Table 3.6-2 表示サイズとバス占有率

# 3.7 オーディオインタフェース

MS-104-SH4AG は、4 チャネルのオーディオインタフェースを備えています。

SH7764 の内蔵シリアルサウンドインタフェース (SSI) を利用し、各種オーディオデコーダに接続して音声データの送受信を行うことができます。

| 機能       | 仕様                                 |

|----------|------------------------------------|

| コネクタ(J7) | 10pin FPC コネクタ XF2M-1015-1A(OMRON) |

|          | -ロック機構                             |

|          | - 0.5mm ピッチ                        |

|          | -上下両接点タイプ                          |

|          | -適合 FPC t=0.3mm                    |

| チャネル数    | 4 チャネル                             |

|          | J6: SSI0,SSI1                      |

|          | J7: SSI2,SSI3                      |

| 動作モード    | 非圧縮モード                             |

|          | トランスミッタ、レシーバ対応                     |

Table 3.7-1 オーディオインタフェース仕様

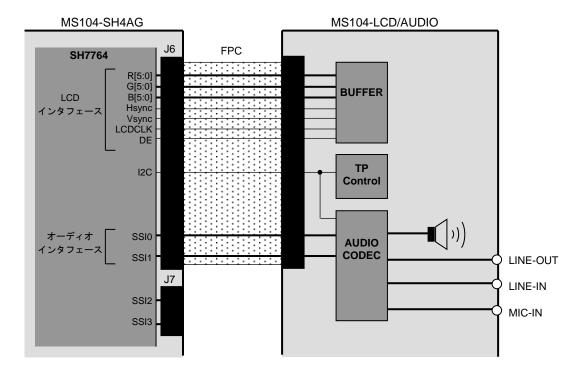

### 3.7.1 外部デバイスとの接続

オーディオインタフェース信号は、FPC コネクタの J6 と J7 にそれぞれ 2 チャネルずつ接続されています。 J6 には、オーディオインタフェース以外に I2C インタフェースおよび LCD インタフェースが接続されており、MS104-LCD/AUDIO に接続することができます。

Fig 3.7-1 MS104-LCD/AUDIO 接続概略図

| No. | 信号名            | 備考          | No. | 信号名            | 備考          |

|-----|----------------|-------------|-----|----------------|-------------|

| 1   | GND            |             | 2   | SSIDATA3/PH4   | 10KΩPULL-UP |

| 3   | SSISCK3/PH5    | 10KΩPULL-UP | 4   | SSIWS3/PH6     | 10KΩPULL-UP |

| 5   | AUDIO_CLK3/PH7 | 10KΩPULL-UP | 6   | GND            |             |

| 7   | SSIDATA2/PC2   | 10KΩPULL-UP | 8   | SSISCK2/PC3    | 10KΩPULL-UP |

| 9   | SSIWS2/PC4     | 10KΩPULL-UP | 10  | AUDIO_CLK2/PC5 | 10KΩPULL-UP |

Table 3.7-2 オーディオインタフェースピンアサイン(J7)

J6 のピンアサインは、「3.6 LCD インタフェース」をご覧ください。

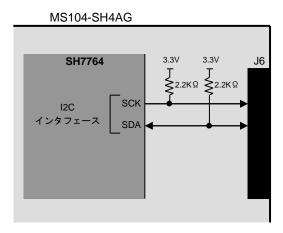

# 3.8 I<sup>2</sup>C インタフェース

MS-104-SH4AG は、 $I^2$ C インタフェースを 1 チャネル備えています。 SH7764 の内蔵  $I^2$ C バスインタフェースを利用し、各種  $I^2$ C 通信デバイスに接続することができます。

| 機能    | 仕様                    |

|-------|-----------------------|

| 転送モード | ファーストモード対応            |

|       | マルチマスタ対応              |

|       | 7 ビット/10 ビットアドレス互換マスタ |

|       | 7 ビットスレーブアドレス         |

Table 3.8-1 I<sup>2</sup>C インタフェース仕様

Fig 3.8-1 I<sup>2</sup>C インタフェース回路概略図

J6 のピンアサインは、「3.6 LCD インタフェース」をご覧ください。

# 3.9 IO ポート

MS-104-SH4AG は、外部接続用に IO ポートが 8 本用意されています。 IO ポートは、CPU の PJO~PJ7 で、コネクタは H-UDI と共用で J5 に接続されています。

| 機能    | No. | 信号名       | I/O | 備考           | No. | 信 <del>号</del> 名 | I/O | 備考           |

|-------|-----|-----------|-----|--------------|-----|------------------|-----|--------------|

| H-UDI | 1   | TCK       | I   | 4.7KΩPULL-UP | 2   | N.C              | -   |              |

|       | 3   | TRST      | I   | 1KΩPULL-DOWN | 4   | MPMD             | I   | 4.7KΩPULL-UP |

|       | 5   | TDO       | 0   |              | 6   | GND              | -   |              |

|       | 7   | ASEBRKAK  | I/O | 4.7KΩPULL-UP | 8   | VCC(3.3V)        | 0   |              |

|       | 9   | TMS       | I   | 4.7KΩPULL-UP | 10  | GND              | -   |              |

|       | 11  | TDI       | I   | 4.7KΩPULL-UP | 12  | GND              | -   |              |

|       | 13  | nRESETOUT | 0   |              | 14  | GND              | -   |              |

| PWR   | 15  | GND       | -   |              | 16  | VCC(3.3V)        | 0   |              |

|       | 17  | GND       | -   |              | 18  | VCC(3.3V)        | 0   |              |

| Ю     | 19  | PJ7       | I/O |              | 20  | PJ6              | I/O |              |

| ポート   | 21  | PJ5       | I/O |              | 22  | PJ4              | I/O |              |

|       | 23  | PJ3       | I/O |              | 24  | PJ2              | I/O |              |

|       | 25  | PJ1       | I/O |              | 26  | PJ0              | I/O |              |

Table 3.9-1 I/O ポートピンアサイン(J5)

#### コネクタについて

J5 は、2 列 2.54mm ピッチ配列(穴径 0.9mm) となっています。

一般的な 2.54mm ピンヘッダやリボンケーブルコネクタが利用できますので、必要に応じて実装してください。

推奨コネクタ: OMRON XG4C シリーズ(XG4C-1034~XG4C-2634)

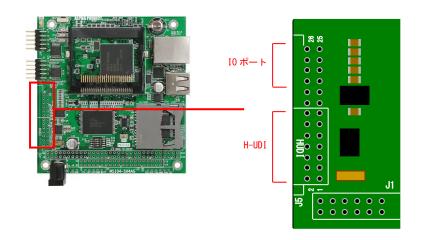

# 3.10 デバッグインタフェース(H-UDI)

MS-104-SH4AG は、プログラムデバッグ用に H-UDI が用意されています。

H-UDI は、SH7764の内蔵デバッグインタフェースで、プログラムのデバッグおよび FLASHROM の書き込みに利用されます。 H-UDI ポートは、IO ポートと共用で J5 に接続されています。(ピンアサインは、3.9 IO ポートを参照してください)

### 3.10.1 H-UDI デバッガの接続

J5 は、未実装となっておりますので、H-UDI を利用する場合にはコネクタを実装する必要があります。標準的な 14pinH-UDI デバッガに接続する場合には、製品付属のコネクタを実装してください。 I0 ポートを使用する場合には、別途 26 ピンのコネクタ等を使用して信号を引き出してください。

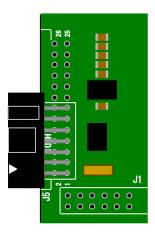

Fig 3.10-1 HUDI コネクタの実装(14pin)

#### TCK について

H-UDI デバッガ等を利用する場合、TCK の設定は 10 MHz 以下を推奨します。 10 MHz 以上で使用した場合、動作が不安定になる場合があります。

### 3.11 PC/104 バスインタフェース

MS104-SH4AG の拡張バスは PC/104 バス配列に準拠しています。(一部未サポート)

PC/104 バスは ISA バスのサブセット版で、PC/104 コンソーシアムで規格化されています。

### 3.11.1 バスモード設定

MS104-SH4AG では、従来の PC/104 バスに準拠した PC/104 バスモードと高速デバイスに対応するための SH バスモードの 2 種類のバスモードを選択できます。バスモードは、ディップスイッチ (SS1-3) で設定します。

ディップスイッチの設定については、「2.8 ディップスイッチ」をご覧ください。

なお、SHバスモードは PC/104 バスボードと互換性がありませんので、ご注意ください。

#### SYSCLK について

PC/104 バスでは、SYSCLK は 8MHz (5.988MHz (Min)  $\sim$ 8.333MHz (Max)) に規定されています。したがって、SYSCLK を必要とする PC/104 周辺ボードを接続する場合には、必ず PC/104 バスモードの設定でご使用ください。

#### SHバスモードについて

PC/104 バスは、ISA バスに準拠しているため、CPU の処理性能に比べて非常に低速です。そのため、オリジナルの回路を接続する場合、PC/104 バスがシステム全体のボトルネックになる場合があります。その問題を解決するための手段として、MS104-SH4AGでは SH バスモードを利用します。

MS104-SH4AG の PC/104 バスのタイミングは、SH7764 のメモリコントローラユニットに依存するため、MCU の設定により、タイミングを調整することができます。

## 3.11.2 アドレスマップ

PC/104 バスには、SH7764 の CS3 空間が割り当てられています。

| CS3 7       | ドレス                   | PC/104 バスアドレス |        |  |

|-------------|-----------------------|---------------|--------|--|

| P0 領域 P2 領域 |                       | メモリ空間         | IO 空間  |  |

| 0x0C000000  | 0xAC000000            | 0x000000      |        |  |

| 0x0CFFFFF   | 0xACFFFFF             | 0xFFFFFF      |        |  |

| 0x0D000000  | 0xAD000000            | -             | 0x0000 |  |

| 0x0D00FFFF  | 0x0D00FFFF 0xAD00FFFF |               | 0xFFFF |  |

Table 3.11-1 PC/104 バスアドレスマップ

#### バス幅の設定について

MS104-SH4AGでは、PC/104のメモリ空間と IO空間が同一 CS空間に割り当てられているため、バス幅は8bitもしくは16bit 固定となります。 (SH7764の CS3 バスコントロールレジスタの設定値に依存します)

したがって、8bit デバイスと 16bit デバイスの混在システムを構築する場合には、注意が必要です。

## 3.11.3 PC/104 バスコネクタ ピンアサイン

| No. |            | J1 LowA                  |      |            | J1 LowB           |     |  |

|-----|------------|--------------------------|------|------------|-------------------|-----|--|

|     | PC/104 信号名 | MS104-SH4AG              | 入出力  | PC/104 信号名 | MS104-SH4AG       | 入出力 |  |

| 1   | IOCHCHK    | Pull-up                  | I    | 0V         | GND               | -   |  |

| 2   | SD7        | D7                       | TI/O | RESETDRV   | CPLD(RESET)       | 0   |  |

| 3   | SD6        | D6                       | TI/O | +5V        | +5V               | 0   |  |

| 4   | SD5        | D5                       | TI/O | IRQ9       | CPLD(IRQ1)        | I   |  |

| 5   | SD4        | D4                       | TI/O | -5V        | -5V               | 0   |  |

| 6   | SD3        | D3                       | TI/O | DRQ2       | NC                | -   |  |

| 7   | SD2        | D2                       | TI/O | -12V       | -12V              | 0   |  |

| 8   | SD1        | D1                       | TI/O | ENDXFR     | pull-up           | I   |  |

| 9   | SD0        | D0                       | TI/O | +12V       | +12V              | 0   |  |

| 10  | IOCHRDY    | CPLD(RDY)                |      | (KEY)      | NC                | -   |  |

| 11  | AEN        | CPLD(CS3 <sup>*1</sup> ) | 0    | SMEMW      | CPLD(WE0/WE1)     | 0   |  |

| 12  | SA19       | A19                      | TO   | SMEMR      | CPLD(RD)          | 0   |  |

| 13  | SA18       | A18                      | TO   | IOW        | CPLD(WE0/WE1)     | TO  |  |

| 14  | SA17       | A17                      | TO   | IOR        | CPLD(RD I/O)      | TO  |  |

| 15  | SA16       | A16                      | TO   | DACK3      | Pull-up           | 0   |  |

| 16  | SA15       | A15                      | TO   | DRQ3       | NC                | I   |  |

| 17  | SA14       | A14                      | TO   | DACK1      | Pull-up           | 0   |  |

| 18  | SA13       | A13                      | TO   | DRQ1       | NC                | I   |  |

| 19  | SA12       | A12                      | TO   | REFRESH    | Pull-up           | 0   |  |

| 20  | SA11       | A11                      | TO   | SYSCLK     | CPLD(7.714286MHz) | I   |  |

| 21  | SA10       | A10                      | TO   | IRQ7       | CPLD(IRQ1)        | I   |  |

| 22  | SA9        | A9                       | TO   | IRQ6       | CPLD(IRQ1)        | I   |  |

| 23  | SA8        | A8                       | TO   | IRQ5       | CPLD(IRQ1)        | I   |  |

| 24  | SA7        | A7                       | TO   | IRQ4       | CPLD(IRQ1)        | I   |  |

| 25  | SA6        | A6                       | TO   | IRQ3       | CPLD(IRQ1)        | I   |  |

| 26  | SA5        | A5                       | TO   | DACK2      | Pull-up           | 0   |  |

| 27  | SA4        | A4                       | TO   | TC         | Pull-up           | OC  |  |

| 28  | SA3        | A3                       | TO   | BALE       | CPLD(BS)          | 0   |  |

| 29  | SA2        | A2                       | TO   | +5V        | +5V               | 0   |  |

| 30  | SA1        | A1                       | TO   | OSC        | Pull-up           | 0   |  |

| 31  | SA0        | A0                       | TO   | 0V         | GND               | -   |  |

| 32  | 0V         | GND                      | -    | 0V         | GND               | -   |  |

| No. |            | J2 LowC       |      |            | J2 LowD     |     |

|-----|------------|---------------|------|------------|-------------|-----|

|     | PC/104 信号名 | MS104-SH4AG   | 入出力  | PC/104 信号名 | MS104-SH4AG | 入出力 |

| 0   | 0V         | GND           | -    | 0V         | GND         | -   |

| 1   | SBHE       | CPLD(CS3)     | TO   | MEMCS16    | Pull-up     | [   |

| 2   | LA23       | A23           | TO   | IOCS16     | Pull-up     | [   |

| 3   | LA22       | A22           | TO   | IRQ10      | CPLD(IRQ1)  | [   |

| 4   | LA21       | A21           | TO   | IRQ11      | CPLD(IRQ1)  | 1   |

| 5   | LA20       | A20           | TO   | IRQ12      | CPLD(IRQ1)  | I   |

| 6   | LA19       | A19           | TO   | IRQ15      | CPLD(IRQ1)  | [   |

| 7   | LA18       | A18           | TO   | IRQ14      | CPLD(IRQ1)  | I   |

| 8   | LA17       | A17           | TO   | DACK0      | Pull-up     | 0   |

| 9   | MEMR       | CPLD(RD)      | TO   | DRQ0       | Pull-up     | [   |

| 10  | MEMW       | CPLD(WE0/WE1) | TO   | DACK5      | Pull-up     | 0   |

| 11  | SD8        | D8            | TI/O | DRQ5       | NC          | [   |

| 12  | SD9        | D9            | TI/O | DACK6      | Pull-up     | 0   |

| 13  | SD10       | D10           | TI/O | DRQ6       | NC          | I   |

| 14  | SD11       | D11           | TI/O | DACK7      | Pull-up     | 0   |

| 15  | SD12       | D12           | TI/O | DRQ7       | NC          | I   |

| 16  | SD13       | D13           | TI/O | +5V        | +5V         | 0   |

| 17  | SD14       | D14           | TI/O | MASTER     | Pull-up     |     |

| 18  | SD15       | D15           | TI/O | 0V         | GND         | -   |

| 19  | (KEY)2     | NC            | -    | 0V         | GND         | -   |

I=入力 O=出力 I/O=入出力 TO=トライステート出力 TI/O=トライステート入出力 OC=オープンコレクタ出力 CPLD(XXXXX) = CPLD を経由して SH7764 の信号に接続されています 未サポート=機能的にサポートされていません Pull-up = Pull-up 抵抗のみに接続されています

Table 3.11-2 PC/104 バスピンアサイン

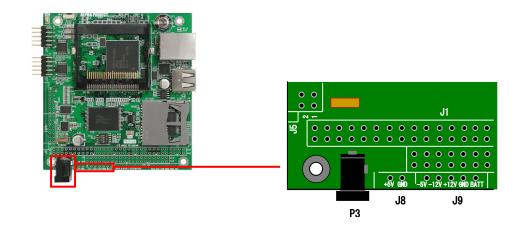

## 3.12 電源

#### 3.12.1 メイン電源

MS104-SH4AG のメイン電源は、DC+5V で、P3 もしくは J8 より供給します。(J8 は未実装です)

消費電流は約500mA以下 (CF, SD カード, USB を除く)ですので、1.0A程度のACアダプタまたは電源を接続してください。PC/104周辺ボードを接続する場合には、最大2.0Aまでの電源を接続できます。

P3 AC アダプタジャック

| No. | 信号名   | 備考           |

|-----|-------|--------------|

| Р   | +5V   | +5V±5% 最大 2A |

| В   | (GND) |              |

| S   | GND   |              |

J8 電源コネクタ(未実装)

| No. | 信号名 | 備考           |

|-----|-----|--------------|

| 1   | +5V | +5V±5% 最大 2A |

| 2   | GND |              |

Fig 3.12-1 電源コネクタ

AC アダプタは、別売の MS104-SH4AG 用の AC アダプタをお勧めします。また、P3 と J8 に別々の電源を同時に接続しないでください。短絡状態となり機器が破損する恐れがあります。

#### 3.12.1 オプション電源

MS104-SH4AG では、+5V 以外の電源を必要としませんが、PC/104 バス規格では、+5V のほかに-5V と+12V と-12V が供給可能となっています。これらは、主にアナログ系入出力ボード等に利用されています。

MS104-SH4AGでは、J9 コネクタから供給可能です。J8 は $\Phi$ 0.9mm のスルーホールで、2.5mm 間隔となっておりますので、適当なコネクタを実装してお使いください。(推奨コネクタ BS5P-SHF-1AA : 日圧) BATT につきましては、RTC(カレンダタイマ)の説明をご覧ください。

| No. | 信号名  | 最大電圧   | 最小電圧   | 最大電流  |

|-----|------|--------|--------|-------|

| 1   | -5V  | -4.75V | -5.25V | 0.2A  |

| 2   | -12V | -11.4V | -12.6V | 0.3A  |

| 3   | +12V | +12.6V | +11.4V | 1.0A  |

| 4   | GND  | -      | -      | -     |

| 5   | BATT | +3.3   | +1.6V  | 0.05A |

Table 3.12-1 電源コネクタ

# 4. テクニカルデータ

## 4.1 外形寸法

Fig 4.1-1 外形寸法図

# 4.2 PC/104 ボードの接続

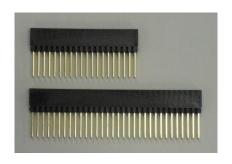

#### 4.2.1 PC/104 コネクタの取り付け

PC/104 周辺ボードを接続する場合には、別売の PC/104 バスコネクタ (64pin 1 個、40pin 1 個) を実装してください。 実装する際には、基板にコネクタをしっかりと差し込んで、浮きがないように取り付けてください。 また、できるだけ細いハンダゴテを使用し、ピンの挿抜部分にハンダが付着しないように注意してください。

Fig 4.2-1 PC/104 コネクタの実装

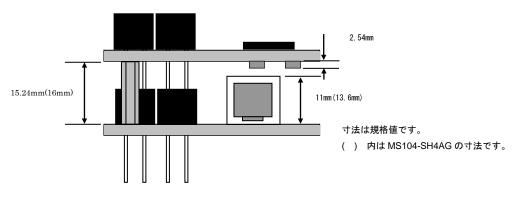

## 4.2.1 PC/104 ボードの接続方法

PC/104 規格準拠ボードは、上下のどちらにでもスタッキングが可能です。

Fig 4.2-2 PC/104 ボードとの接続例

#### MS104-SH4AG のスタッキング接続に関する注意

MS104-SH4AG は、LAN コネクタの実装高さが PC/104 規格寸法を超えています。(上図参照)。そのため、MS104-SH4AG の上に周辺ボードをスタッキングする場合、規格値 15mm のスペーサーを使用すると上の基板部品と干渉する恐れがあります。したがって、MS104-SH4AG の上にスタッキングする場合には、添付の 16mm のスペーサーを使用してください。それでも部品が干渉する場合には、連結用に PC/104 コネクタのみを 1 段分入れるなどしてください。

Fig 4.2-3 PC/104 スタッキング寸法図

# 4.3 DC 特性

### 4.3.1 PC/104 インタフェース

| 信号名  | シンボル | パラメータ        | Min   | Max   |

|------|------|--------------|-------|-------|

| 入力電圧 | VIH  | High レベル入力電圧 | 2. 0V | 5. 5V |

|      | VIL  | Low レベル入力電圧  | OV    | 0. 8V |

| 出力電圧 | Vон  | High レベル出力電圧 | 2. 4V |       |

|      | VoL  | Low レベル出力電圧  |       | 0. 4V |

Table 4.3-1 PC/104 インタフェース DC 特性

# 4.3.2 IO ポート、LCD インタフェース、オーディオインタフェース

| 項目        | シンボル              | パラメータ        | MIN    | TYP   | MAX    |

|-----------|-------------------|--------------|--------|-------|--------|

| 入力電圧      | $V_{\mathrm{IH}}$ | High レベル入力電圧 | 2. 0V  |       | 3. 6V  |

|           | V <sub>IL</sub>   | Low レベル入力電圧  | -0. 3V |       | 0. 66V |

| 出力電圧      | V <sub>OH</sub>   | High レベル出力電圧 | 2. 4V  |       |        |

|           | $V_{0L}$          | Low レベル出力電圧  |        |       | 0. 55V |

| プルアップ抵抗*1 | R <sub>PULL</sub> |              | 20 KΩ  | 60 KΩ | 180 KΩ |

<sup>\*1</sup> プルアップ抵抗は SH7764 のポートコントロールレジスタで有無の選択ができます。

Table 4.3-2 IO ポート、LCD インタフェース、オーディオインタフェース DC 特性

### 4.3.3 I<sup>2</sup>C インタフェース

| 項目      | シンボル              | パラメータ        | MIN    | TYP     | MAX    |

|---------|-------------------|--------------|--------|---------|--------|

| 入力電圧    | V <sub>IH</sub>   | High レベル入力電圧 | 2. 31V |         | 3. 6V  |

|         | V <sub>IL</sub>   | Low レベル入力電圧  | -0. 3V |         | 0. 99V |

| 出力電圧    | V <sub>OL</sub>   | Low レベル出力電圧  |        |         | 0. 4V  |

| プルアップ抵抗 | R <sub>PULL</sub> |              |        | 2. 2 KΩ |        |

Table 4.3-3 I<sup>2</sup>C インタフェース DC 特性

# 5. 関連製品のご案内

## 5.1 Linux 開発キット

MS104-SH4AGでのLinuxシステム開発に必要なものがすべてセットになっていますので、すぐに開発に取りかかることができます。Linux開発環境に仮想マシンを採用していますので、Windows上で開発をおこなうことができます。

#### キット内容

#### DVD-ROM

- -Linux クロス開発環境

- ・ブートローダソースコード

- ・カーネルソースコード

- ・デバイスドライバソースコード

- ・GNU C クロスコンパイラ

- ・サンプルプログラム

- 解説マニュアルー式

Ethernet ケーブル

RS232 ケーブル

CFメモリカード

AC アダプタ

# 5.2 MS104 シリーズ機能拡張ボード

MS104-SH4AGに機能拡張ボードを接続することで、簡単にさまざまな機能を追加することができます。

MS104-LCD/AUDIO は、MS104-SH4AG 専用 WQVGA タッチパネル付 LCD 搭載、LCD・オーディオボードです。TFT 4.3 inch WQVGA タッチパネル付 LCD、スピーカーを標準搭載し、ステレオヘッドフォン出力、ステレオライン入力、ステレオマイク入力機能など、AV 機能を追加できます。

MS104-FPGA/CⅢ

Intel 社製 FPGACycloneⅢ EP3C16F484 を搭載した、PC/104 バス準拠のFPGA ボードです。

FLASHROM と SDRAM を搭載しており、汎用 FPGA ボードや NIOS II プロセッサボードとして利用することもできます。

# 5.3 AC アダプタ

MS104-SH4AGで使用できるACアダプタです。

| 項目  | 仕様                      |

|-----|-------------------------|

| 入力  | AC100V                  |

| 出力  | DC5V/2A                 |

| その他 | RoHS 対応                 |

|     | PSE <mark>認定取得済み</mark> |

# 5.4 PC/104 コネクタ

PC/104 バスに使用する PC/104 コネクタのセットです。

| PC/104 コネクタセット-L    |  |  |

|---------------------|--|--|

| ハンダ付けタイプ            |  |  |

| 端子長さ 23.25mm        |  |  |

| 64pin 1 個 40pin 1 個 |  |  |

| RoHS 対応             |  |  |

| PC/104 コネクタセット-S    |  |  |

|---------------------|--|--|

| ハンダ付けタイプ            |  |  |

| 端子長さ 3.2mm          |  |  |

| 64pin 1 個 40pin 1 個 |  |  |

| RoHS 対応             |  |  |

# 5.5 Flash 書き込みツール

FlashWriterEX は、SH-2/3/4 用の Flash 書き込みソフトで約 1000 種類以上の FlashROM と FlashROM 内蔵型マイコンに対応しています。ユーザシステムのバージョンアップソフトの配布に便利なライティングモジュール作成機能等も備えており開発から量産用途まで、幅広くご利用いただけます。

# 6. 製品サポートのご案内

#### ●ユーザ登録

ユーザ登録は弊社ホームページにて受け付けております。ユーザ登録をしていただきますと、バージョンアップや最新の情報等を E-Mail でご案内させていただきますので、是非ご利用ください。

弊社ホームページアドレス https://www.apnet.co.jp

#### ●修理の依頼

修理をご依頼いただく場合は、下記サイトにある製品保証規定と修理規定をご確認の上、「お問い合わせフォーム」より製品サポートへご連絡ください。

修理・故障に関するお問い合わせ

https://www.apnet.co.jp/support/index.html

#### ●製品サポートの方法

製品サポートについては、FAX もしくは E-Mail でのみ受け付けております。お電話でのお問い合わせは受け付けておりませんのでご了承ください。なお、お問い合わせの際には、製品名、使用環境、使用方法等、問題点などを詳細に記載してください。

#### 技術的なお問い合わせ

E-Mail query@apnet.co.jp

以下の内容に該当するお問い合わせにつきましては受け付けておりませんのであらかじめご了承ください。

- ■本製品の回路動作及びCPUおよび周辺デバイスの使用方法に関するご質問

- ■ユーザ回路の設計方法やその動作についてのご質問

- ■関連ツールの操作指導

- ■その他、製品の仕様範囲外の質問やお客様の技術によって解決されるべき問題

#### ●ソフトウェアのサポート

<u>ソフトウェアに関する技術的な質問は、受け付けておりませんのでご了承ください。</u> サポートをご希望されるお客様には、個別に有償にて承りますので弊社営業までご相談ください。

# エンジニアリングサービスのご案内

弊社製品をベースとしたカスタム品やシステム開発を承っております。 お客様の仕様に合わせて、設計から OEM 供給まで一貫したサービスを提供いたします。 詳しくは、弊社営業窓口までお問い合わせください。

#### 営業案内窓口

| TEL    | 053-401-0033(代表)  |

|--------|-------------------|

| FAX    | 053-401-0035      |

| E-Mail | sales@apnet.co.jp |

# 改定履歴

| 版数   | 日付         | 改定内容                                                                  |

|------|------------|-----------------------------------------------------------------------|

| 1版   | 2008/12/10 | 新規作成                                                                  |

| 2版   | 2008/12/24 | 「Table 1.3-1 使用概要」消費電流を記載                                             |

|      |            | 「Table 4.3-3 I <sup>2</sup> C インタフェース DC 特性」修正                        |

| 3版   | 2009/01/06 | 「Fig 2.8-1 ディップスイッチの設定」修正                                             |

| 4版   | 2010/02/01 | 「Table 3.9-1 I/O ポートピンアサイン(J5)」コネクタ番号修正                               |

|      |            | 「Fig 2.4-1 制御レジスタ一覧」制御レジスタ 0 H'AD400000 に修正                           |

|      |            | 「Table 2.1-3 IO ポートの機能割り当て(2)」                                        |

|      |            | -PIO の信号名を修正                                                          |

|      |            | -PF7, PF6, PF5 のピンファンクション設定と機能を修正                                     |

| _ #= |            | 「FIg 1.4-1 外観」J3とJ4の表記誤りを修正                                           |

| 5版   | 2010/04/26 | 「2.6.1 EEPROM のインタフェース」誤記修正                                           |

| 6版   | 2021/02/05 | 「梱包内容」変更                                                              |

|      |            | 「取り扱い上の注意」修正                                                          |

|      |            | 「保証」修正<br>「参考 URL」 更新                                                 |

|      |            | 「Table1.3-1」、「Fig1.5-1」、「2.3章」                                        |

|      |            | -SDRAM 型番を K4S561632-UC75 (Samsung) から M12L2561616A-6TIG2S (ESMT) に変更 |

|      |            | 「2.7.4 外部割込みマスクとステータス」制御レジスタ 10 DO, D1, D2, D3 の表記誤りを修正               |

|      |            | ルネサステクノロジの社名をルネサスエレクトロニクスに変更                                          |

|      |            | Spansion の社名を Cypress に変更                                             |

|      |            | ALTERA の社名を Intel に変更                                                 |

|      |            | 「5.1 Linux 開発キット」修正                                                   |

|      |            | 「6. 製品サポートのご案内」更新                                                     |

|      |            | 「エンジニアリングサービスのご案内」更新                                                  |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

|      |            |                                                                       |

## 参考文献

「SH7764 グループハードウェアマニュアル」 ルネサス エレクトロニクス株式会社 その他 各社データシート

### 本文書について

- ・本文書の著作権は株式会社アルファプロジェクトが保有します。

- ・本文書の内容を無断で転載することは一切禁止します。

- ・本文書の内容は、将来予告なしに変更されることがあります。

- ・本文書の内容については、万全を期して作成いたしましたが、万一ご不審な点、誤りなどお気付きの点がありましたら弊社までご連絡ください。

- ・本文書の内容に基づき、アプリケーションを運用した結果、万一損害が発生しても、弊社では一切責任を負いませんのでご了承ください。

### 商標について

- ・SH-4A および SH7764 は、ルネサス エレクトロニクス株式会社の登録商標、商標または商品名称です。

- ・その他の会社名、製品名は、各社の登録商標または商標です。

株式会社アルファプロジェクト 〒431-3114 静岡県浜松市東区積志町834 https://www.apnet.co.jp E-Mail:query@apnet.co.jp