SH-2 SH7144F CPU ボード

# AP-SH2F-7A

# ハードウェアマニュアル

8 版

## ご使用になる前に

このたびは AP-SH2F-7A をお買い上げいただき誠にありがとうございます。 本製品をお役立て頂くために、このマニュアルを十分お読みいただき、正しくお使いください。 今後共、弊社製品をご愛顧賜りますよう宜しくお願いいたします。

## **梱包内容**

本製品は、下記の品より構成されております。梱包内容をご確認のうえ、万が一、不足しているものがあればお買い上げの販売店までご連絡ください。

AP-SH2F-7A 梱包内容

●AP-SH2F-7A

1枚

●電源ハーネス (2Pin)

1本

●マニュアル・サンプルプログラムのダウンロード・保証のご案内

1枚

■本製品の内容及び仕様は予告なしに変更されることがありますのでご了承ください。

## 取り扱い上の注意

●本製品には、民生用の一般電子部品が使用されており、一般的な民生用途の電子機器への使用を意図して 設計されています。宇宙、航空、医療、原子力、運輸、交通、各種安全装置などで人命、事故に関わる 用途および多大な物的損害を発生させる恐れのある用途でのご使用はご遠慮ください。

- ●極端な高温下や低温下、または振動の激しい環境での使用はご遠慮ください。

- ●水中、高湿度、油の多い環境でのご使用はご遠慮ください。

- ●腐食性ガス、可燃性ガス等の環境中でのご使用はご遠慮ください。

- ●基板の表面が水に濡れていたり、金属に接触した状態で電源を投入しないでください。

- ●定格を越える電源を加えないでください。

- ■ノイズの多い環境での動作は保証しかねますのでご了承ください。

- ■連続的な振動(車載等)や衝撃が発生する環境下でのご使用は、製品寿命を縮め、故障が発生しやすくなりますのでご注意ください。

- ■発煙や発火、異常な発熱があった場合には、すぐに電源を切ってください。

- ■本製品を仕様範囲を越える条件において使用した場合、故障の原因となりますので、ご注意ください。

- ■本書に記載される製品および技術のうち、「外国為替および外国貿易法」に定める規制貨物等(技術)に該当するものを輸出または 国外に持ち出す場合には同法に基づく輸出許可が必要です。

- ■本製品マニュアル、回路図の著作権は株式会社アルファプロジェクトが保有しております。これらを無断で転用、掲載、 譲渡、配布することは禁止します。

## 保証

- ■保証期間内において、本マニュアル等に記載の注意事項に従い正常な使用状態で故障した場合、保証対象といたします。

- ■製品保証の内外を問わず、製品を運用した結果による、直接的および間接的損害については、弊社は一切補償いたしません。

- ■保証対象は、製品本体とします。ソフトウェア・マニュアル・消耗品・梱包箱は保証対象外とさせていただきます。

- ■本保証は日本国内においてのみ有効です。海外からのご依頼は受付しておりません。

- ■製品保証規定の詳細につきましては、ホームページをご覧ください。

## 目 次

| 1. | 製品紹介                     |     |  |  |  |  |

|----|--------------------------|-----|--|--|--|--|

|    |                          |     |  |  |  |  |

|    | 1. 1 製品概要                |     |  |  |  |  |

|    | 1. 2 機能及び特長              | 1   |  |  |  |  |

| 2. | 仕様概要                     | 3   |  |  |  |  |

|    |                          |     |  |  |  |  |

|    |                          | 3   |  |  |  |  |

|    | -· - / 1 // 2            | 4   |  |  |  |  |

|    |                          | 5   |  |  |  |  |

|    | 2. 4 回路構成                | 6   |  |  |  |  |

|    | 2. 5 アドレスマップ             | 7   |  |  |  |  |

| 3. |                          | 10  |  |  |  |  |

|    |                          |     |  |  |  |  |

|    | 3. 1 CPU 動作モードの設定        | 1 0 |  |  |  |  |

|    | 3. 2 SRAM の設定            | 1 3 |  |  |  |  |

|    |                          | 1 4 |  |  |  |  |

|    | 3. 4 ボード供給電源の選択          | 1 4 |  |  |  |  |

|    | 3. 5 モニタLEDの設定           | 1 5 |  |  |  |  |

|    | 3. 6 メモリバックアップ           | 1 6 |  |  |  |  |

|    | 3. 7 リセット                |     |  |  |  |  |

|    |                          |     |  |  |  |  |

| 4. | コネクタ                     | 18  |  |  |  |  |

|    |                          |     |  |  |  |  |

|    | 4. 1 コネクタの端子配列           |     |  |  |  |  |

|    | 4. 2 推奨コネクタ              |     |  |  |  |  |

|    | 4.3 外部回路との拡張方法           | 2 1 |  |  |  |  |

| 5. | 技術資料                     | 2 2 |  |  |  |  |

|    |                          |     |  |  |  |  |

|    | 5. 1 内蔵 FlashROM の書き込み方法 | 2 2 |  |  |  |  |

|    | 5. 2 回路図                 | 2 4 |  |  |  |  |

| 6. | 関連製品のご案内                                                                        | 2 5                      |

|----|---------------------------------------------------------------------------------|--------------------------|

|    | 6. 1 通信アダプタ<br>6. 2 インテリジェント SD カードリーダライタ<br>6. 3 Flash 書き込みツール<br>6. 4 デバッグツール | 2 5<br>2 5<br>2 6<br>2 6 |

| 7. | その他                                                                             | 2 7                      |

■製品サポートのご案内

■エンジニアリングサービスのご案内

## 1. 製品紹介

## 1. 1 製品概要

AP-SH2F-7A は、CPU コアに SH-2 を採用したシングルチップマイコン「SH7144F」を搭載した汎用 CPU ボードです。本ボードは外部接続コネクタへ外部拡張に必要な信号をすべて引き出してありますので、各種試作用途及び小ロットの製品への適用など、幅広い対応が可能です。

### 1.2 機能及び特長

#### ■32 ビット RISC CPU「SH7144F」(ルネサス エレクトロニクス)を搭載

<SH7144F 概要>

- ・内部 32 ビット構成

- 256Kbyte FlashROM 内蔵

- ・8Kbyte RAM 内蔵

- · 乗算器内蔵

- パイプライン 5段パイプライン

- ・DMA コントローラ 4 チャネル

- ・データトランスファコントローラ

- ・マルチファンクションタイマパルスユニット 16 ビット 5 チャネル

- ・コンペアマッチタイマ 16 ビット 2 チャネル

- ・ウォッチドックタイマ 8ビット

- ・シリアルインターフェース 4チャネル

- ・割り込み 外部9本 (NMI、IRQ7~IRQ0)

- ・パラレルポート 最大 82 本 (兼用端子含む 入出力 74 本 入力 8 本)

- ・A/D 変換器 分解能 10 ビット 8 チャネル

- ·最高動作周波数 50MHz (PLL 使用時)

- · 低消費電力

※機能詳細は SH7144F のハードウェアマニュアルをご参照下さい。

#### ■内蔵FlashROM 256KByte、内蔵RAM 8KByte、高速SRAM 1MByte搭載

本製品に採用したSH7144FはFlashROMを256KByte内蔵しています。

内蔵FlashROMは、1ステートアクセスなのでSH-2の性能を最大限に引き出せます。RAMは内蔵RAM8KByteに加え、外部にバックアップ可能な高速SRAMを16bitバス幅接続で1MByte搭載しておりますので、多種多様な使い方が可能です。

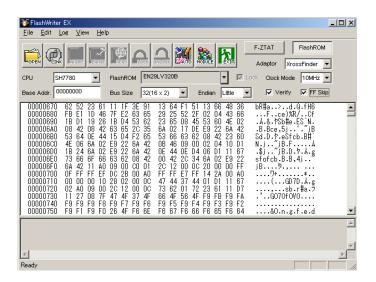

## ■Flash書き込みソフト付属

FlashWriterEX for SH7144Fが付属しています。

#### ■H-UDI 用コネクタを装備

H-UDI 用の 14Pin コネクタを装備しておりますので、JTAG 環境でのデバッグが容易に行えます。

#### ■通信用コネクタを装備

シリアル I/F コネクタを装備しておりますので、外付けに RS232 アダプタ(PC-RS-04 別売)や、USB アダプタ(PC-USB-04 別売)、LAN アダプタ(PC-LAN-02 別売)などを接続することで、簡単に PC との通信が行えます。

## ■外部拡張が容易

外部接続用コネクタ (50Pin×2 未実装) へ拡張に必要な信号線をすべて引き出してありますので、I/O 等の接続が容易です。

#### ■組込みに便利なコンパクトサイズ

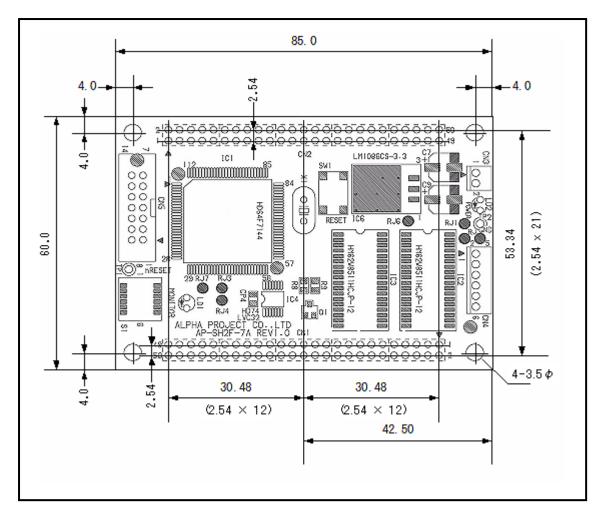

基板は、85×60 (mm) と小型なので機器の組み込みにも最適です。

# 2. 仕様概要

## 2. 1 仕様概要

## AP-SH2F-7A 仕様

| 項目        | 仕 様                                                                      |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------|--|--|--|--|--|

| CPU       | SH7144F、ルネサス エレクトロニクス社製                                                  |  |  |  |  |  |

| 動作周波数     | 最大 49. 152MHz (12. 288MHz 水晶)                                            |  |  |  |  |  |

| メモリ       | 内蔵 FlashROM 256KByte<br>内蔵 RAM 8KByte<br>外部 SRAM 1MByte (バッテリバックアップ可)    |  |  |  |  |  |

| シリアル I/F  | 非同期/同期 I/F 4チャネル                                                         |  |  |  |  |  |

| パラレル I/O  | 82 本(兼用端子を含む)                                                            |  |  |  |  |  |

| タイマ/カウンタ  | 16 ビットマルチファンクションタイマ 5 チャネル<br>16 ビットコンペアマッチタイマ 2 チャネル<br>8 ビットウォッチドッグタイマ |  |  |  |  |  |

| 割り込み      | 割り込みコントローラ内蔵<br>外部 9本 (NMI, IRQ7~IRQ0)                                   |  |  |  |  |  |

| A/D コンバータ | 8 チャネル 分解能 10bit                                                         |  |  |  |  |  |

| リセット      | リセット IC, リセット SW 搭載<br>外部拡張コネクタ(未実装)からのリセットも可能                           |  |  |  |  |  |

| 外部接続      | 外部拡張 50Pin コネクタ×2 未実装 H-UDI 14Pin コネクタ シリアル I/F 6Pin コネクタ 電源 2Pin コネクタ   |  |  |  |  |  |

| 電源電圧      | DC 5.0V±5%/3.3V±5%<br>外部からの 3.3V供給動作可能                                   |  |  |  |  |  |

| 消費電流      | MAX 420mA                                                                |  |  |  |  |  |

| 使用環境条件    | 温度 0~50℃<br>湿度 20~80% (結露なし)                                             |  |  |  |  |  |

| 寸法        | 85×60 (mm)                                                               |  |  |  |  |  |

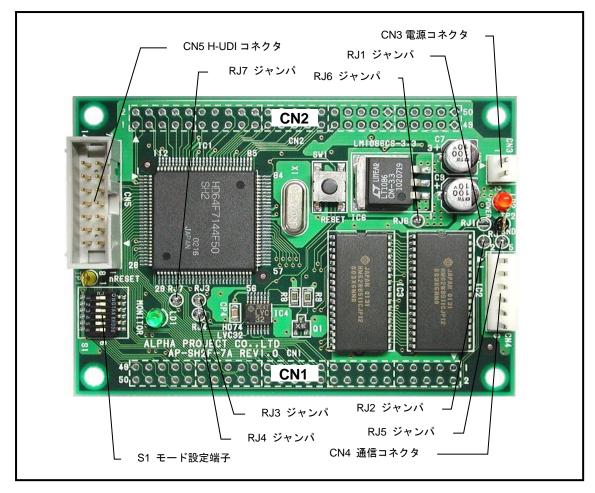

## 2. 2 外観

Fig 2.2-1 外形図

| コネクタ番号 | コネクタ型番/メーカー     | 用途         | 備考  |

|--------|-----------------|------------|-----|

| CN1    | XG4H-5031/オムロン  | バス拡張コネクタ   | 未実装 |

| CN2    | XG4H-5031/オムロン  | I/0 拡張コネクタ | 未実装 |

| CN3    | B2P-SHF-1AA/日圧  | 電源コネクタ     |     |

| CN4    | B6P-SHF-1AA/日圧  | 通信コネクタ     |     |

| CN5    | 7614-6002/住友 3M | H-UDI コネクタ |     |

Table 2.2-1 コネクタ一覧

## 2. 3 外形寸法

Fig 2.3-1 外形寸法図

$CN1 \cdot CN2$  は 2.54mm ピッチの格子上にスルーホールが配置されています。 外部回路を増設されるお客さまは、市販のユニバーサルボードをご使用いただけます。 (Fig 4-3-1 をご覧ください。)

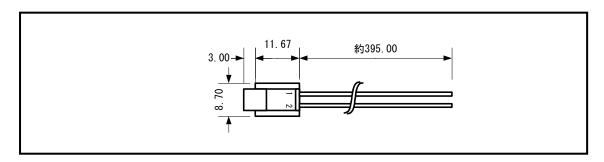

Fig 2.3-2 電源ハーネス外形寸法図

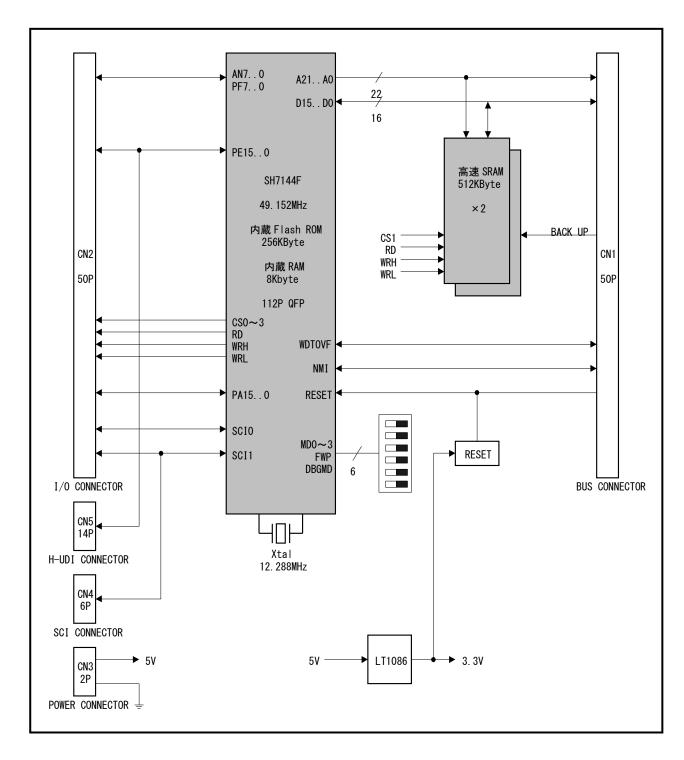

## 2. 4 回路構成

Fig 2.4-1 回路構成

## 2. 5 アドレスマップ

## 2. 5. 1 SRAM バス幅 16bit 時

本ボードでは、CS1に SRAM がアサインされています。 動作モードの設定については「3.1 CPU 動作モードの設定」を参照してください。 SRAM バス幅の設定については「3.2.2 SRAM バス幅の選択」を参照してください。

| アドレス       | デバイス                 | 領域     | 備考 |

|------------|----------------------|--------|----|

| H'00000000 | 内蔵 FlashROM 256KByte |        |    |

| H'0003FFFF |                      |        |    |

| H'00040000 | 予約                   | _      |    |

| H'001FFFFF |                      |        |    |

| H'00200000 | ユーザ開放                | CSO 空間 |    |

| H'003FFFFF |                      |        |    |

| H'00400000 | SRAM (16bit) 1MByte  | CS1 空間 |    |

| H'004FFFFF |                      |        |    |

| H'00500000 | イメージ                 |        |    |

| H'007FFFFF |                      |        |    |

| H'00800000 | ユーザ開放                | CS2 空間 |    |

| H'00BFFFFF |                      |        |    |

| H'00C00000 |                      | CS3 空間 |    |

| H'00FFFFF  |                      |        |    |

| H'01000000 | 予約                   | _      |    |

| H'FFFF7FFF |                      |        |    |

| H'FFFF8000 | 周辺 I/0               | _      |    |

| H'FFFFBFFF |                      |        |    |

| H'FFFFC000 | 予約                   | _      |    |

| H'FFFFDFFF |                      |        |    |

| H'FFFFE000 | 内蔵 RAM 8KByte        | _      |    |

| H'FFFFFFF  |                      |        |    |

Table 2.5-1 SRAM バス幅 16bit の時(出荷時設定) CPU 動作モード(2、F2)

## !注意

SH7144F はリセット後、A18~A21 がポート端子となっています。

本メモリマップどおりに動作させるためには、リセット直後に A18~A19 をアドレス端子として機能するように、 PFC を初期化する必要があります。

## 2. 5. 2 SRAM バス幅 8bit 時

動作モードの設定については「3.1 CPU動作モードの設定」を参照してください。 SRAM バス幅の設定については「3.2.2 SRAM バス幅の選択」を参照してください。

| アドレス       | デバイス                 | 領域     | 備考 |

|------------|----------------------|--------|----|

| H'00000000 | 内蔵 FlashROM 256KByte | _      |    |

| H'0003FFFF |                      |        |    |

| H'00040000 | 予約                   | _      |    |

| H'001FFFFF |                      |        |    |

| H'00200000 | ユーザ開放                | CSO 空間 |    |

| H'003FFFFF |                      |        |    |

| H'00400000 | SRAM (8bit) 512KByte | CS1 空間 |    |

| H'0047FFFF |                      |        |    |

| H'00480000 | イメージ                 |        |    |

| H'007FFFFF |                      |        |    |

| H'00800000 | ユーザ開放                | CS2 空間 |    |

| H'00BFFFFF |                      |        |    |

| H'00C00000 |                      | CS3 空間 |    |

| H'00FFFFF  |                      |        |    |

| H'01000000 | 予約                   | _      |    |

| H'FFFF7FFF |                      |        |    |

| H'FFFF8000 | 周辺 I/0               | _      |    |

| H'FFFFBFFF |                      |        |    |

| H'FFFFC000 | 予約                   | _      |    |

| H'FFFFDFFF |                      |        |    |

| H'FFFFE000 | 内蔵 RAM 8KByte        | _      |    |

| H'FFFFFFF  |                      |        |    |

Table 2.5-2 SRAM バス幅 8bit の時 CPU 動作モード (2、F2)

## !注意

SH7144F はリセット後、A18~A21 がポート端子となっています。

本メモリマップどおりに動作させるためには、リセット直後に A18 をアドレス端子として機能するように、PFC を初期化する必要があります。

## 2. 5. 3 シングルチップ時

動作モードの設定については「3.1 CPU動作モードの設定」を参照してください。

| アドレス       | デバイス                 | 領域 | 備考 |

|------------|----------------------|----|----|

| H'00000000 | 内蔵 FlashROM 256KByte | _  |    |

| H'0003FFFF |                      |    |    |

| H'00040000 | 予約                   | _  |    |

|            |                      |    |    |

| H'FFFF7FFF |                      |    |    |

| H'FFFF8000 | 周辺 I/0               | _  |    |

| H'FFFFBFFF |                      |    |    |

| H'FFFFC000 | 予約                   | _  |    |

| H'FFFFDFFF |                      |    |    |

| H'FFFFE000 | 内蔵 RAM 8KByte        | _  |    |

| H'FFFFFFF  |                      |    |    |

Table 2.5-3 シングルチップの時 CPU 動作モード (3、F3)

## 2. 5. 4 ウェイト設定

本ボード上のメモリアクセスのウェイト数は以下の設定を推奨します。

|          |                      | システ             |                 |                 |             |

|----------|----------------------|-----------------|-----------------|-----------------|-------------|

|          | メモリ種別                | ×1<br>12.288MHz | ×2<br>24.576MHz | ×4<br>49.152MHz | チップ<br>セレクト |

|          |                      | 12.200IVITZ     | 24.37 0IVITZ    | 49. IOZIVITZ    |             |

| FlashROM | 内蔵 FlashROM          | _               | -               | _               | -           |

| SRAM     | HM62W8511HCJP-12 相当品 | OWAIT           | OWAIT           | 1WAIT           | CS1         |

Table 2.5-4 メモリアクセスのウェイト数

## ! 注意

内蔵 FlashROM は NO-WAIT となります。

## 3. 機能説明

本ボードは、使用用途に応じてさまざまな設定の変更が行えます。お客様の用途に合わせて最適な設定にしてください。なお、設定を変更する際には必ず電源を切ってから行ってください。

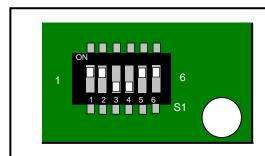

## 3. 1 CPU 動作モードの設定

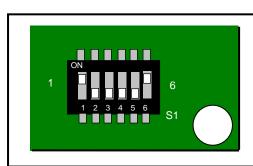

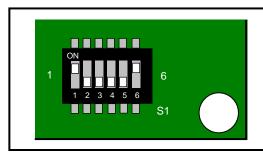

SH7144Fには、モード設定端子があり CPU 動作モード及びデバッグモードの設定をします。AP-SH2F-7A では、S1 で設定します。

<出荷時設定>

CPU 動作モード : MODE 2

クロックモード : クロックモード3(S: ×4:P: ×2)

デバッグモード : 非デバッグモード

Fig 3.1-1 S1 の設定

| S1    | 1     | 2   | 3   | 4   | 5   | 6   |

|-------|-------|-----|-----|-----|-----|-----|

| 端子名   | DBGMD | FWP | MD3 | MD2 | MD1 | MDO |

| 出荷時設定 | ON    | OFF | OFF | OFF | OFF | ON  |

Table 3.1-1 S1 接続端子

## !注意

動作モードの設定は、必ず電源を切った状態で行ってください。

## 3. 1. 1 CPU 動作モードの選択

SH7144Fには様々な動作モードがあります。本ボードでは以下のモード設定が可能です。

|      |            | S1 設定      |            |                          | <b>++</b> | 000        |

|------|------------|------------|------------|--------------------------|-----------|------------|

| MODE | 2<br>(FWP) | 5<br>(MD1) | 6<br>(MD0) | モード名                     | 内蔵<br>ROM | CS0<br>バス幅 |

| 0    | OFF        | ON         | ON         | MCU 拡張モード O              | 無効        | 8          |

| 1    | OFF        | ON         | OFF        | MCU 拡張モード 1              | 無効        | 16         |

| 2    | OFF        | OFF        | ON         | MCU 拡張モード2               | 有効        | 8/16       |

| 3    | OFF        | OFF        | OFF        | シングルチップモード               | 有効        | _          |

| F0   | ON         | ON         | ON         | ブートモード                   | 有効        | 8/16       |

| F1   | ON         | ON         | OFF        | ブートモード<br>(シングルチップ)      | 有効        | _          |

| F2   | ON         | OFF        | ON         | ユーザプログラムモード              | 有効        | 8/16       |

| F3   | ON         | OFF        | OFF        | ユーザプログラムモード<br>(シングルチップ) | 有効        | _          |

Table 3.1-2 CPU 動作モードの設定

## !注意

動作モードの変更は、各ジャンパの設定と周辺インターフェースの接続をよく確認のうえ行ってください。 上記以外の設定はしないでください。

## 3. 1. 2 クロックモードの選択

SH7144F はクロック逓倍用 PLL 回路を内蔵しており、以下のクロックモードが設定可能です。

| MODE   | S1 [ | 没定  | \ -   L - L |            |  |

|--------|------|-----|-------------|------------|--|

| MODE 3 |      | 4   | システムクロック    | 周辺クロック     |  |

| 0      | ON   | ON  | × 1         | × 1        |  |

| 1      | ON   | OFF | $\times 2$  | $\times 2$ |  |

| 2      | 0FF  | ON  | $\times 4$  | $\times 4$ |  |

| 3      | 0FF  | 0FF | $\times 4$  | $\times 2$ |  |

Table 3.1-3 クロックモードの設定

## !注意

SH7144F は 40MHz を超える周辺クロックでの動作を保証していませんので、標準搭載の振動子(12.288MHz)を使用する場合には、MODE2 は設定できません。

## 3. 1. 3 デバッグモードの選択

SH7144F は、H-UDI 端子を備えており JTAG(H-UDI)デバッガを接続することができます。デバッガを接続するためには、CPU を デバッグモードにする必要があります。

| S1-1 | モード      | 備考    |

|------|----------|-------|

| ON   | 非デバッグモード | 出荷時設定 |

| OFF  | デバッグモード  |       |

Table 3.1-4 デバッグモードの設定

## 3. 2 SRAM の設定

## 3. 2. 1 SRAM 使用/未使用の選択

本ボードには 1MByte ( $512K \times 8bit \times 2$  個) の高速 SRAM が実装されています。 SRAM のチップセレクトには CS1 が接続されていますが、CS1 空間を他の目的で使用する場合には切り離すことが可能です。

#### RJ3 設定

短絡: SRAM (CS1) を使用する (出荷時設定)

未短絡 : SRAM (CS1) を使用しない

Fig 3.2-1 RJ3 設定

## 3. 2. 2 SRAM バス幅の選択

SRAM は CPUに 16 ビットバス幅で接続されていますが、PD8~15 をポートとして使用する場合には切り離すことが可能です。

#### RJ1、RJ2、RJ4 設定

| RJ1 | RJ2 | RJ4 | バス幅設定          |

|-----|-----|-----|----------------|

| 未短絡 | 短絡  | 短絡  | 16 ビット幅(出荷時設定) |

| 短絡  | 未短絡 | 未短絡 | 8 ビット幅         |

Table 3.2-1 RJ1、RJ2、RJ4 設定

#### !注意

8 ビット幅の設定では SRAM の総容量は 512KByte になります。

## 3. 3 シリアル通信 I/F CTS・RTS 設定

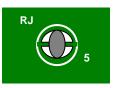

SH7144F の SCI にはフロー制御用の RTS/CTS 端子はありません。しかし、接続する相手機器には RTS と CTS を必要とするものがあります。それらの機器と通信を行うために、シリアル通信 I/F の RTS・CTS の短絡を RJ5 にて設定可能です。

#### RJ5 設定

短絡 : RTS と CTS を短絡する (出荷時設定)

未短絡 : RTS と CTS を短絡しない

Fig 3.3-1 RJ5 設定

## !注意

本処理は簡易的なものでフロー制御を実現するものではありません。したがって、接続する機器によってデータオー バーフロー等が発生する場合があります。

## 3. 4 ボード供給電源の選択

本ボードでは、5V からボード上のレギュレータで 3.3V を生成していますが、外部から直接 3.3V の電源を供給することも可能です。5V を供給する場合には CN3 から、3.3V は CN1 もしくは CN2 から供給します。

#### RJ6 設定

短絡: 5Vを供給(レギュレータを使用)する(出荷時設定)

未短絡 : 3.3V を供給する

Fig 3.4-1 RJ6 設定

## ! 注意

各電源は必ず所定のコネクタより供給してください。

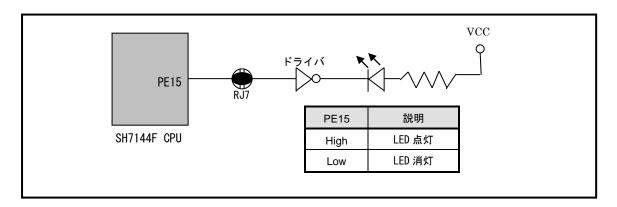

## 3.5 モニタ LED の設定

本ボードには、簡易テスト用にモニタ LED (LD1: 緑) が実装されています。 ポートは PE15 を使用していますが、使用しない場合には切り離すことが可能です。

## RJ7 設定

短絡 : モニタ LED を使用する(出荷時設定)

未短絡 : モニタ LED を使用しない

Fig 3.5-1 RJ7 設定

Fig 3.5-2 モニタ LED の接続

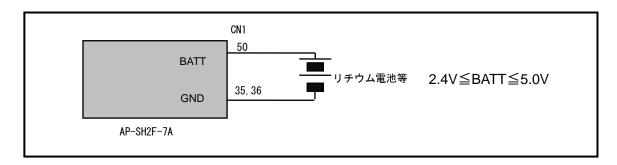

## 3.6 メモリバックアップ

本ボード上の RAM は外部にバックアップ電源を接続することによりバックアップが可能です。 BATT 端子 (CN1 50P) にバックアップ電源を接続してください。 なお、リチウムイオン電池等の 2 次電池を使用される場合には、別途充電回路が必要となります。

Fig 3.6-1 メモリバックアップ接続

#### !注意

本ボードで採用している高速 SRAM は、バックアップ電流に typ2.5mA/max5mA が必要です。

## 3. 7 リセット

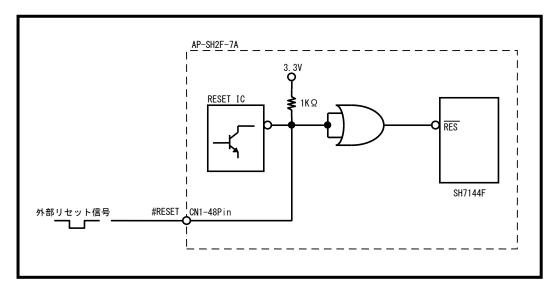

本ボードのリセット動作には以下の3つがあります。

#### 1) 電源投入時及び電圧降下時のリセット動作

5V 供給時に 3.3V レギュレータ出力が約  $2.75V \sim 3.05V$  (標準 2.9V) でシステムリセットされます。 #RESET 端子は専用 IC(PST592IM (ミツミ製)) により、約 100ms 間の Low パルスが出力されます。 CPU はパワーオンリセット例外処理を開始します。

#### 2) リセットSWによるリセット動作

リセット SW を押すことにより強制的にシステムリセットされます。 こちらも専用 IC により約 100ms 間の Low パルスが出力されますので、CPU は、パワーオンリセット例外処理を開始します。

#### 3) 外部からの制御によるリセット

#RESET 端子 (CNI 48P) へ外部回路を接続することにより、外部からのリセット動作が可能となります。 #RESET 信号はオープンコレクタ出力なのでワイアード OR 接続が可能です。 この場合は、外部のリセット回路により、安定時間分のリセット信号を Low レベルに保持する必要があります。

Fig 3.7-1 リセット内部回路

## 4. コネクタ

## 4. 1 コネクタの端子配列

本ボードは外部拡張に必要な信号を CN1、CN2 にすべて引き出してあります。 以下に各コネクタの端子配列を示します。

CN1 CPUバスコントロール系信号コネクタ

| No | 信号名                  | 備考                  | No | 信号名                  | 備考               |

|----|----------------------|---------------------|----|----------------------|------------------|

| 1  | D15/PD15/#AUDSYNC    | 10KΩ プ <i>ル</i> アップ | 2  | D14/PD14/AUDCK       | 10K Ω 7° N7 y 7° |

| 3  | D13/PD13/AUDMD       | 10KΩ プルアップ          | 4  | D12/PD12/#AUDRST     | 10K Ω 7° N7 y 7° |

| 5  | D11/PD11/AUDATA3     | 10KΩ プ <i>ル</i> アップ | 6  | D10/PD10/AUDATA2     | 10K Ω 7° N7 y 7° |

| 7  | D9/PD9/AUDATA1       | 10KΩ プルアップ          | 8  | D8/PD8/AUDATA0       | 10KΩ 7° N7y7°    |

| 9  | D7/PD7               | 10KΩ プ <i>ル</i> アップ | 10 | D6/PD6               | 10KΩ 7° N7y7°    |

| 11 | D5/PD5               | 10KΩ プ <i>ル</i> アップ | 12 | D4/PD4               | 10KΩ 7° N7y7°    |

| 13 | D3/PD3               | 10KΩ 7° N7y7°       | 14 | D2/PD2               | 10KΩ 7° N7ッ7°    |

| 15 | D1/PD1               | 10KΩ プルアップ          | 16 | DO/PDO               | 10KΩ 7° N7y7°    |

| 17 | 3. 3V                |                     | 18 | 3. 3V                |                  |

| 19 | A21/PB9/#IRQ7/#ADTRG |                     | 20 | A20/PB8/#IRQ6/#WAIT  |                  |

| 21 | A19/PB7/#IRQ5/#BREQ  | 10K Ω プ ルダ ウン       | 22 | A18/PB6/#IRQ4/#BACK  | 10KΩ プルダウン       |

| 23 | PB5/#IRQ3/#P0E3      |                     | 24 | PB4/#IRQ2/#P0E2      |                  |

| 25 | PB3/#IRQ1/#P0E1/SDA0 |                     | 26 | PB2/#IRQ0/#P0E0/SCL0 |                  |

| 27 | A17/PB1              |                     | 28 | A16/PB0              |                  |

| 29 | A15/PC15             |                     | 30 | A14/PC14             |                  |

| 31 | A13/PC13             |                     | 32 | A12/PC12             |                  |

| 33 | A11/PC11             |                     | 34 | A10/PC10             |                  |

| 35 | GND                  |                     | 36 | GND                  |                  |

| 37 | A9/PC9               |                     | 38 | A8/PC8               |                  |

| 39 | A7/PC7               |                     | 40 | A6/PC6               |                  |

| 41 | A5/PC5               |                     | 42 | A4/PC4               |                  |

| 43 | A3/PC3               |                     | 44 | A2/PC2               |                  |

| 45 | A1/PC1               |                     | 46 | AO/PCO               |                  |

| 47 | #WDTOVF              |                     | 48 | #RESET               | 1K Ω 7° N7ッ7°    |

| 49 | NMI                  | 10K Ω 7° ルアッフ°      | 50 | BATT                 |                  |

信号名に#がついているものは負論理をあらわします。

CN2 CPU I/O系信号コネクタ

| No | 信号名                       | 備考               | No | 信号名                    | 備考                                                                                                       |

|----|---------------------------|------------------|----|------------------------|----------------------------------------------------------------------------------------------------------|

| 1  | PE15/TIOC4D/DACK1/#IRQOUT | 10K Ω 7° ルアッフ°   | 2  | PE14/TIOC4C/DACKO      | 10K Ω 7° N7y7°                                                                                           |

| 3  | PE13/TIOC4B/#MRES         | 10KΩ プルアップ       | 4  | PE12/TIOC4A/TXD3       | 10K Ω 7° N7y7°                                                                                           |

| 5  | PE11/TIOC3D/RXD3          | 10K Ω 7° ルアッフ°   | 6  | PE10/TIOC3C/TXD2       | 10K Ω 7° N7y7°                                                                                           |

| 7  | PE9/TIOC3B/SCK3           | 10K Ω 7° ルアッフ°   | 8  | PE8/TIOC3A/SCK2        | 10K Ω 7° N7y7°                                                                                           |

| 9  | PE7/TIOC2B/RXD2           | 10KΩ プルアップ       | 10 | PE6/TIOC2A/SCK3        | 10K Ω 7° N7y7°                                                                                           |

| 11 | PE5/TIOC1B/TXD3           | 10K Ω 7° ルアッフ°   | 12 | _                      |                                                                                                          |

| 13 | 3. 3V                     |                  | 14 | 3. 3V                  |                                                                                                          |

| 15 | PF7/AN7                   |                  | 16 | PF6/AN6                |                                                                                                          |

| 17 | PF5/AN5                   |                  | 18 | PF4/AN4                |                                                                                                          |

| 19 | PF3/AN3                   |                  | 20 | PF2/AN2                |                                                                                                          |

| 21 | PF1/AN1                   |                  | 22 | PF0/AN0                |                                                                                                          |

| 23 | VCC (5V)                  |                  | 24 | VCC (5V)               |                                                                                                          |

| 25 | PE4/TIOC1A/RXD3/TCK       | 4. 7K Ω 7° N7y7° | 26 | PE3/TIOCOD/DRAK1/TD0   | 4. 7K Ω 7° Nアッフ°                                                                                         |

| 27 | PE2/TIOCOC/#DREQ1/TDI     | 4. 7K Ω 7° N7y7° | 28 | PE1/TIOCOB/DRAKO/#TRST | 4. $7$ K $\Omega$ $7$ ° $ν$ $7$ $ν$ $7$                                                                  |

| 29 | PEO/TIOCOA/#DREQO/TMS     | 4. 7K Ω 7° Nアッフ° | 30 | _                      |                                                                                                          |

| 31 | PA15/CK                   | 10KΩ プルアップ       | 32 | PA14/#RD               | $10 \mathrm{K}\Omega$ 7° $\nu$ 7 $\gamma$ 7°                                                             |

| 33 | PA13/#WRH                 | 10KΩ プルアップ       | 34 | PA12/#WRL              | $10 \mathrm{K}\Omega$ 7° $\nu$ 7 $\gamma$ 7°                                                             |

| 35 | PA11/#CS1                 | 10K Ω 7° ルアッフ°   | 36 | PA10/#CS0              | $10 \mathrm{K}\Omega$ $\mathcal{I}^{\circ}$ $\mathcal{N}\mathcal{T}$ $_{\mathcal{I}}\mathcal{T}^{\circ}$ |

| 37 | PA9/#IRQ3/TCLKD           | 10K Ω 7° ルアッフ°   | 38 | PA8/#IRQ2/TCLKC        | 10K Ω 7° N7y7°                                                                                           |

| 39 | GND                       |                  | 40 | GND                    |                                                                                                          |

| 41 | PA7/#CS3/TCLKB            | 10K Ω 7° ルアッフ°   | 42 | PA6/#CS2/TCLKA         | 10K Ω 7° N7y7°                                                                                           |

| 43 | PA5/#IRQ1/SCK1/#DREQ1     | 10K Ω 7° ルアッフ°   | 44 | PA4/TXD1               | 10K Ω 7° N7y7°                                                                                           |

| 45 | PA3/RXD1                  | 10KΩ プルアップ       | 46 | PA2/#IRQO/SCKO/#DREQO  | 10K Ω 7° N7y7°                                                                                           |

| 47 | PA1/TXD0                  | 10KΩ プルアップ       | 48 | PAO/RXDO               | 10K Ω 7° N7y7°                                                                                           |

| 49 | GND                       |                  | 50 | GND                    |                                                                                                          |

信号名に#がついているものは負論理をあらわします。

CN3 電源コネクタ

| No. | 信号名 |

|-----|-----|

| 1   | +5V |

| 2   | GND |

CN4 シリアル通信 I / Fコネクタ

| No. | 信号名   |

|-----|-------|

| 1   | RXD   |

| 2   | TXD   |

| 3   | RTS   |

| 4   | CTS   |

| 5   | 3. 3V |

| 6   | GND   |

CN5 H‐UDIコネクタ

| No. | 信号名         |

|-----|-------------|

| 1   | PE4(TCK)    |

| 2   | PE1 (#TRST) |

| 3   | PE3 (TD0)   |

| 4   | #ASEBRKAK   |

| 5   | PEO (TMS)   |

| 6   | PE2(TDI)    |

| 7   | #CPU_RES    |

| 8   | GND         |

| 9   | GND         |

| 10  | GND         |

| 11  |             |

| 12  | GND         |

| 13  | GND         |

| 14  | GND         |

信号名に#がついているものは負論理をあらわします。

SH7144Fには兼用端子が多数存在するため注意して下さい。各信号の機能は SH7144F のデータシートをご覧下さい。

## 4. 2 推奨コネクタ

CN1、CN2 用のコネクタは CPU ボードオプション品 (拡張コネクタセット) として取り扱いしておりますのでお問い合わせください。

CN1、2 : 推奨コネクタ : XG4H-5031 (オムロン)

適合レセプタクル : XG4C-5031 (オムロン)

CN3 : 使用コネクタ : B2P-SHF-1AA (日圧)

適合レセプタクル : H2P-SHF-AA (日圧)

CN4 : 使用コネクタ : B6P-SHF-1AA (日圧)

適合レセプタクル : H6P-SHF-AA (日圧)

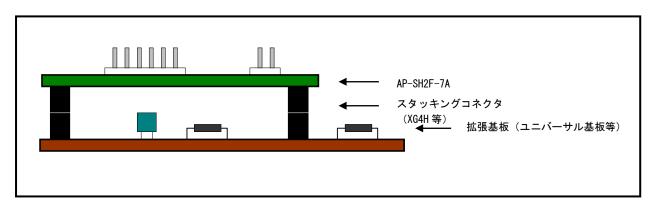

## 4. 3 外部回路との拡張方法

外部に回路を拡張する場合には、スタッキング接続が最も一般的な方法です。

リボンケーブル等で接続する方法もありますが、長さに比例して信号が劣化しますので注意してください。

本ボードの拡張コネクタは全て 2.54mm ピッチで配置されているので、拡張の基板には市販のユニバーサル基板が使用できます。

Fig 4.3-1 外部回路の拡張

## 5. 技術資料

## 5. 1 内蔵 FlashROM の書き込み方法

SH7144F は 256KByte の FlashROM を内蔵しています。内蔵 FlashROM は付属の FlashWriterEX for SH7144F を利用してオンボード で書き込みが可能です。

FlashWriterEX for SH7144F 使用時のパソコン側の動作環境を次に示します。

| 対応 OS | Windows 10/11 |

|-------|---------------|

| ポート   | シリアルポート 1ch   |

Table 5.1-1 パソコン側の動作環境

FlashWriterEX for SH7144F 使用時のボード側の動作環境を次に示します。

Table 5.1-2 ボード側の動作環境

#### 1) ボードの準備

モードの設定

CPU 動作モードを以下の設定に合わせます。設定は電源を切った状態で行ってください。

### S1 内蔵 FlashROM 書き込み時の設定

CPU 動作モード : ブートモード (F0)

クロックモード : クロックモード  $3(S: \times 4: P: \times 2)$

デバッグモード : 非デバッグモード

Fig 5.1-1 動作モードの設定

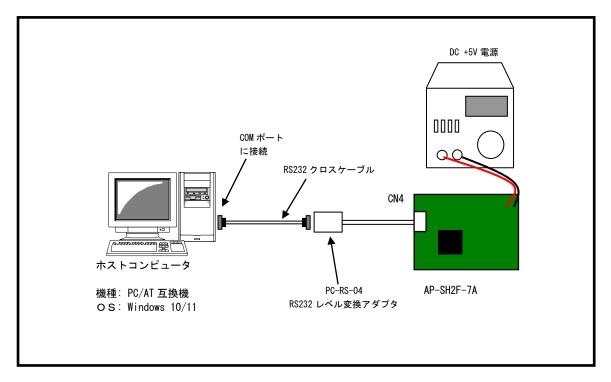

#### 2) パソコンと CPU ボードの接続

パソコンと CPU ボードを RS232 クロスケーブルと RS232 レベル変換アダプタで接続します。

Fig 5.1-2 FlashWriterEX for SH7144F 使用時の接続例

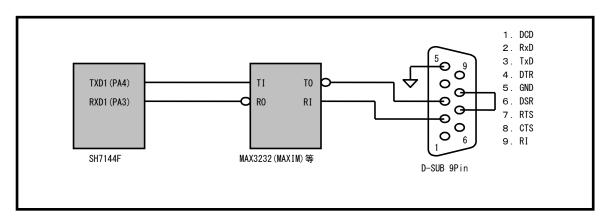

弊社の RS232 変換アダプタ (PC-RS-04) を使用しない場合には、シリアル出力を外部回路にて RS232 レベル に変換する必要があります。

Fig 5.1-3 SCI の設計例

#### 3) FlashWriterEX for SH7144F を使用しての書き込み

FlashWriterEX を用いた書き込み方法は、アプリケーションノート「AN141 ボード付属 FlashWriterEX を使った内蔵 FlashROM への書き込み方法」を参照してください。

「AN141 ボード付属 FlashWriterEX を使った内蔵 FlashROM への書き込み方法」は、弊社ホームページより入手できます。

#### 4)動作の確認

動作確認は次の手順で実行してください。

①モードの設定

CPU 動作モードを以下の設定に合わせます。設定は電源を切った状態で行ってください。

#### S1 サンプルプログラム動作時の設定

CPU 動作モード : MODE2

クロックモード : クロックモード 3 (S: ×4: P: ×2)

デバッグモード: 非デバッグモード

Fig 5.1-4 動作モードの設定

②電源を投入すると、プログラムが動作します。

\*サンプルプログラムの動作内容に関しては、アプリケーションノート「AN126 サンプルプログラム解説」を参照してください。

「AN126 サンプルプログラム解説」は、弊社ホームページより入手できます。

## 5. 2 回路図

回路図は、弊社ホームページよりダウンロードできます。

詳しくは、製品添付の 「マニュアル・サンプルプログラムのダウンロード・保証のご案内」をご覧ください。

## 6. 関連製品のご案内

## 6. 1 通信アダプタ

通信コネクタ(CN4)に通信アダプタを接続することで、さまざまな通信に対応することができます。

| 製品名          | 製品機能                | 備考         |

|--------------|---------------------|------------|

| PC-RS-04     | TTL⇔RS232 コンバータ     | 3.3V/5V 対応 |

| PC-USB-04    | シリアル⇔USB コンバータ      | 3.3V/5V 対応 |

| PC-LAN-02    | シリアル⇔LAN コンバータ      | 3.3V/5V 対応 |

| PC-RS485-01A | TTL⇔RS422/485 コンバータ | 3.3V/5V 対応 |

※2023年10月現在の状況となっており、予告なしに変更される場合があります。

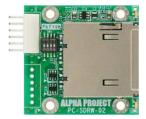

## 6. 2 インテリジェント SD カードリーダライタ

PC-SDRW-02 は、アルファボードシリーズのシリアル I/F に接続するインテリジェント SD カードリーダライタです。 本製品を使用することにより、CPU ボードへ簡単にストレージ機能を付加することが可能です。

| 製品名        | 製品機能         | 備考          |

|------------|--------------|-------------|

| PC-SDRW-02 | SD カードリーダライタ | 3. 3V/5V 対応 |

PC-SDRW-02

※2023年10月現在の状況となっており、予告なしに変更される場合があります。

## 6. 3 Flash 書き込みツール

FlashWriterEX は、SH-2/3/4 用の Flash 書き込みソフトで 800 種類以上の FlashROM と FlashROM 内蔵型のマイコンに対応しています。ユーザシステムのバージョンアップソフトの配布に便利なライティングモジュール作成機能等も備えており開発から量産用途まで、幅広くご利用いただけます。

\* H-UDI インターフェースとして、「XrossFinder」または「HJ-LINK」が必要です。

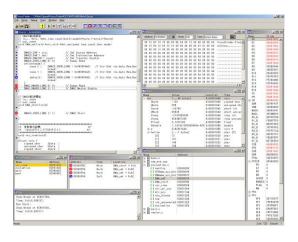

## 6. 4 デバッグツール

JTAG デバッガ「XrossFinder」は、ルネサス エレクトロニクス SuperH マイコン SH-2/3/4 に対応した JTAG (H-UDI) デバッガです。

小型で USB バスパワーに対応しているので省スペースで快適なデバッグ環境を実現しています。

GNU C/C++、ルネサス エレクトロニクス製 C/C++ クロスコンパイラに対応しています。

低価格なので、初めて導入される方や大量に導入を検討されているお客様にも最適です。

## 7. その他

## 製品サポートのご案内

### ●ユーザ登録

ユーザ登録は弊社ホームページにて受け付けております。ユーザ登録をしていただきますと、バージョンアップや最新の情報等を E-Mail でご案内させていただきますので、是非ご利用ください。

弊社ホームページアドレス <a href="https://www.apnet.co.jp">https://www.apnet.co.jp</a>

#### ●修理の依頼

修理をご依頼いただく場合は、下記サイトにある製品保証規定と修理規定をご確認の上、「お問い合わせフォーム」より 製品サポートへご連絡ください。

#### 修理・故障に関するお問い合わせ

https://www.apnet.co.jp/support/index.html

#### ●製品サポートの方法

製品サポートについては、FAX もしくは E-Mail でのみ受け付けております。お電話でのお問い合わせは受け付けておりませんのでご了承ください。なお、お問い合わせの際には、製品名、使用環境、使用方法等、問題点などを詳細に記載してください。

### 技術的なお問い合わせ

E — M a i I <u>query@apnet.co.jp</u>

以下の内容に該当するお問い合わせにつきましては受け付けておりませんのであらかじめご了承ください。

- ■本製品の回路動作及びCPUおよび周辺デバイスの使用方法に関するご質問

- ■ユーザ回路の設計方法やその動作についてのご質問

- ■関連ツールの操作指導

- ■その他、製品の仕様範囲外の質問やお客様の技術によって解決されるべき問題

#### ●ソフトウェアのサポート

<u>ソフトウェアに関する技術的な質問は、受け付けておりませんのでご了承ください。</u> サポートをご希望されるお客様には、個別に有償にて承りますので弊社営業までご相談ください。

# エンジニアリングサービスのご案内

弊社製品をベースとしたカスタム品やシステム開発を承っております。 お客様の仕様に合わせて、設計から OEM 供給まで一貫したサービスを提供いたします。 詳しくは、弊社営業窓口までお問い合わせください。

#### 営業案内窓口

| TEL    | 053-401-0033 (代表) |

|--------|-------------------|

| FAX    | 053-401-0035      |

| E-Mail | sales@apnet.co.jp |

Alpha Board Series AP-SH2F-7A

# 改定履歴

| 版数 | 日付         | 改定内容                               |

|----|------------|------------------------------------|

| 初版 | 2003/01/14 | 新規作成                               |

| 2版 | 2003/08/28 | PC-RS-03 を PC-RS-04 に変更(全体)        |

| 3版 | 2004/02/17 | 2. 1 2) SRAM設定 SRAMバス幅の選択表を修正      |

| 4版 | 2005/04/22 | 3.3 3) 図3-2 SCIの設計例を修正             |

|    |            | PC-USB-01 を PC-USB-02 に変更(全体)      |

| 5版 | 2007/07/30 | 全体の書式を変更                           |

| 6版 | 2008/12/16 | Table 3-1-2 CPU 動作モードの設定表を修正       |

|    |            | 関連製品のご案内を更新(6章)                    |

| 7版 | 2020/12/04 | 梱包内容 変更                            |

|    |            | 「取り扱い上の注意」修正                       |

|    |            | 「保証」修正                             |

|    |            | ルネサステクノロジの社名をルネサスエレクトロニクスに変更       |

|    |            | PC-USB-02A を PC-USB-04 に変更(全体)     |

|    |            | 対応 OS を更新(5章)                      |

|    |            | PC-LAN-01 を PC-LAN-02 に変更(6.1章)    |

|    |            | PC-SDRW-01 を PC-SDRW-01A に変更(6.2章) |

|    |            | 製品サポートのご案内を更新(7章)                  |

|    |            | エンジニアリングサービスのご案内を更新(7章)            |

| 8版 | 2023/10/02 | 対応 OS を更新(5章)                      |

|    |            | 関連製品のご案内を更新(6章)                    |

|    |            | 住所を更新                              |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

|    |            |                                    |

Alpha Board Series AP-SH2F-7A

## 参考文献

「SH7144 グループハードウェアマニュアル」 ルネサス エレクトロニクス株式会社 その他 各社データシート

## 本文書について

- ・本文書の著作権は株式会社アルファプロジェクトが保有します。

- ・本文書の内容を無断で転載することは一切禁止します。

- ・本文書の内容は、将来予告なしに変更されることがあります。

- ・本文書の内容については、万全を期して作成いたしましたが、万一ご不審な点、誤りなどお気付きの点がありましたら弊社までご連絡ください。

- ・本文書の内容に基づき、アプリケーションを運用した結果、万一損害が発生しても、弊社では一切責任を負いませんのでご了承ください。

## 商標について

- ・SH-2 および SH7144 は、ルネサス エレクトロニクス株式会社の登録商標、商標または商品名称です

- ・Windows®の正式名称は Microsoft®Windows®Operating System です。

- ・Microsoft、Windows は、米国 Microsoft Corporation.の米国およびその他の国における商標または登録商標です。

- ・Windows®10、Windows®11 は、米国 Microsoft Corporation.の商品名称です。

- ・本文書では下記のように省略して記載している場合がございます。ご了承ください。 Windows®10 は Windows 10 もしくは Win10

Windows®11 はWindows 11 もしくはWin11

・その他の会社名、製品名は、各社の登録商標または商標です。

株式会社アルファプロジェクト

〒431-3114 静岡県浜松市中央区積志町834 https://www.apnet.co.jp E-Mail:query@apnet.co.jp