# MS104-FPGA/CⅢ サンプル HDL プログラム解説

2.1版 2023年10月02日

## 1. 概要

#### 1.1 概要

本アプリケーションノートは MS104-FPGA/CⅢに付属するサンプル HDL プログラムについて解説します。 MS104-FPGA/CⅢには下記のサンプルプログラムが付属しています。

| サンプル HDL プログラム                  | 動作内容                     |

|---------------------------------|--------------------------|

| PC/104 バス用サンプル HDL プログラム(SLABE) | ・PC/104 バス I/0 空間アクセス    |

|                                 | ・PC/104 バス MEMORY 空間アクセス |

詳細な動作内容に関しては、後述の「4.動作説明」を参照してください。

#### 1.2 設定

本サンプルHDLプログラムはMS104-FPGA/CⅢと、マスタとなるPC/104規格準拠CPUボード(弊社製MS104-SH4AG、MS104-SH4、MS104-SH2等)で動作します。MS104-FPGA/CⅢの設定スイッチは出荷時設定としてください。マスタボードの設定等につきましては、マスタボードのマニュアル等を参照してください。

### 1.3 開発環境について

本サンプル HDL プログラムは FPGA/CPLD 開発ソフトウェア Quartus II を用いて開発されています。サンプル HDL プログラム に対応する開発環境は以下のようになります。

| フォルダ              | 開発環境       | バージョン             |

|-------------------|------------|-------------------|

| ms104-fpga_sample | Quartus II | Version8.0 SP1 以降 |

※ Quartus II Web Edition は Intel 社のウェブサイトからダウンロードできます。

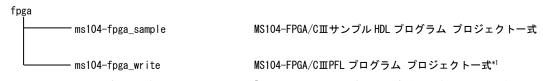

## 2. サンプル HDL プログラムの構成

弊社 Web サイトにて公開している MS104-FPGA/CⅢのサンプル HDL プログラムは、下記のようなフォルダ構成になっています。 サンプル HDL プログラムはあらかじめ Quartus Ⅱのワークフォルダにコピーし、開発を行ってください。

\*1 PFL についての詳細はアプリケーションノート「AN1201 FLASHROM の書き込み方法」を参照してください。

Fig 2-1 サンプル HDL プログラムの構成

## 3. プロジェクトファイルの読み込み

①Quartus II を起動します。

Fig 3-1 Quartus II の起動

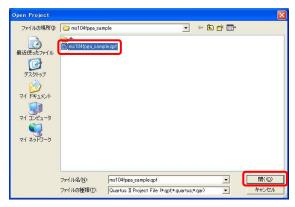

②Quartus II の[File]メニューから[Open Project]を選択し、Quartus II のワークフォルダ内の [fpga] - [ms104-fpga\_sample] 内にある「ms104-fpga\_sample.qpf」ファイルを選択します。

Fig 3-2 プロジェクトファイルの選択

③以上でプロジェクトファイルの読み込みは完了です。Quartus II の詳細な使用方法につきましては、Quartus II のマニュアル 等を参照してください。

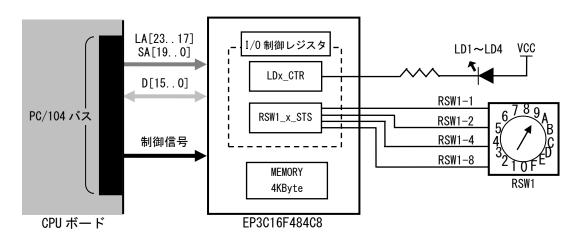

# 4. 動作説明

### 4.1 サンプル HDL プログラム動作説明

本サンプル HDL プログラムは以下の動作を行います。

| 項目                  | 動作                                 |  |  |

|---------------------|------------------------------------|--|--|

| PC/104 バス I/0 空間    | ・LED (LD1~LD4) の点灯/消灯制御            |  |  |

|                     | ・ロータリスイッチ (RSW1) のポジションの読み出し       |  |  |

| PC/104 バス MEMORY 空間 | ・FPGA 内に 4KByte のメモリを持ち、リード/ライトが可能 |  |  |

Table 4-1 サンプル HDL プログラム動作説明

Fig 4-1 サンプル HDL プログラム動作構成図

## 4.2 アドレスマップ

| 空間        | アドレス      | 機能             | ビット幅  |

|-----------|-----------|----------------|-------|

| I/0 空間    | Н' 000000 | I/0 制御レジスタ     | 16bit |

|           | H' 000001 |                |       |

|           | H' 000002 | 未使用            |       |

|           | H'FFFFFF  |                |       |

| MEMORY 空間 | Н' 000000 | メモリ領域 (4KByte) | 16bit |

|           | H' 000FFF |                |       |

|           | H' 001000 | 未使用            |       |

|           | H'FFFFFF  |                |       |

Table 4-2 アドレスマップ

### 4.3 I/0制御レジスタ

本サンプルプログラムでは MS104-FPGA/CⅢの LED 制御、RSW1 のモニタ用の I/O 制御レジスタがあります。

| ビット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|-----|----|----|----|----|----|----|---|---|

| 名称  | -  | -  | -  | ı  | ı  | -  | - | - |

| 初期値 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

| R/W | R  | R  | R  | R  | R  | R  | R | R |

| ビット | 7       | 6       | 5       | 4       | 3          | 2          | 1          | 0          |

|-----|---------|---------|---------|---------|------------|------------|------------|------------|

| 名称  | LD4_CTR | LD3_CTR | LD2_CTR | LD1_CTR | RSW1_8_STS | RSW1_4_STS | RSW1_2_STS | RSW1_1_STS |

| 初期値 | 0       | 0       | 0       | 0       | -          | -          | -          | -          |

| R/W | R/W     | R/W     | R/W     | R/W     | R          | R          | R          | R          |

Table 4-3 I/0 制御レジスタ

| ビット  | ビット名称      | 初期値 | R/W | 機能            |

|------|------------|-----|-----|---------------|

| 15~8 | -          | 0   | R   | 未使用           |

| 7~4  | LDx_CTR    | 0   | R/W | 0:LDx 消灯      |

|      |            |     |     | 1:LDx 点灯      |

| 3~0  | RSW1_x_STS | -   | R   | 0:RSW1_x HIGH |

|      |            |     |     | 1:RSW1_x LOW  |

Table 4-4 レジスタの説明

| ポジション | RSW1_8_STS | RSW1_4_STS | RSW1_2_STS | RSW1_1_STS |

|-------|------------|------------|------------|------------|

| 0     | 0          | 0          | 0          | 0          |

| 1     | 0          | 0          | 0          | 1          |

| 2     | 0          | 0          | 1          | 0          |

| 3     | 0          | 0          | 1          | 1          |

| 4     | 0          | 1          | 0          | 0          |

| 5     | 0          | 1          | 0          | 1          |

| 6     | 0          | 1          | 1          | 0          |

| 7     | 0          | 1          | 1          | 1          |

| 8     | 1          | 0          | 0          | 0          |

| 9     | 1          | 0          | 0          | 1          |

| Α     | 1          | 0          | 1          | 0          |

| В     | 1          | 0          | 1          | 1          |

| С     | 1          | 1          | 0          | 0          |

| D     | 1          | 1          | 0          | 1          |

| E     | 1          | 1          | 1          | 0          |

| F     | 1          | 1          | 1          | 1          |

Table 4-5 RSW1 のポジションに対する RSW1\_x\_STS の値

## ご注意

- ・本文書の著作権は株式会社アルファプロジェクトが保有します。

- ・本文書の内容を無断で転載することは一切禁止します。

- ・本文書の内容は、将来予告なしに変更されることがあります。

- ・本文書に記載されている内容についての質問等のサポートは一切受け付けておりませんのでご了承ください。

- ・本文書の内容については、万全を期して作成いたしましたが、万一ご不審な点、誤りなどお気付きの点がありましたら弊社までご連絡 ください。

- ・本文書の内容に基づき、アプリケーションを運用した結果、万一損害が発生しても、弊社では一切責任を負いませんのでご了承ください。

### 商標について

- ・CycloneⅢは Intel Corporation の登録商標、商標または商品名称です。

- ・その他の会社名、製品名は、各社の登録商標または商標です。

株式会社アルファプロジェクト

〒431-3114 静岡県浜松市中央区積志町 834 https://www.apnet.co.jp E-Mail: query@apnet.co.jp